잉여 리셋 제거로 전력소비와 면적을 절약한다

글/모힛 쿠마르(Mohit Kumar)

심층 순차분석이 높은 가치를 갖는 이유

리셋은 하드웨어를 알려진 상태로 강제 초기화 하는 것으로서, 설계 착수 시 또는 오류 복구를 위해 실행된다. 오늘날의 SoC 디자인에서는 리셋 기능을 갖춘 레지스터가 수백만 개 탑재되어 있는 경우도 드물지 않게 볼 수 있다. 유감스럽게도, 이러한 리셋들 중 다수는 불필요한 잉여적 존재들이다. 이 불필요한 레지스터 리셋들을 디자인 내에 그대로 남겨두면 전력소비가 늘어나고 면적이 과도하게 커지며 배선이 혼잡해진다. 하지만 리셋을 사실상 필요로 하지 않는 레지스터가 어떤 것인지 알아내기란 극히 어려운 일이다. 전통적으로, 디자이너는 수작업적인 기법을 이용해 잉여 레지스터를 찾아낸다. 그러나 정말로 필요한 것은 자동화된 접근 방법이다.

잉여 리셋의 문제점

전력효율적인 디자인은 오늘날의 일차적인 설계목표 중 하나이다. 리셋을 갖춘 레지스터에는 보다 큰 기술(Technology) 셀이 요구되며, 이로 인해 디자인에 소요되는 면적과 전력도 증가하게 된다. 레지스터에 리셋 기능이 있는 경우와 없는 경우의 간단한 예를 비교해 보자.

프리셋(preset)과 클리어(clear)를 추가하기 위해서는 3입력 NAND 게이트가 요구되며, 이는 레지스터의 면적과 전력소비를 크게 증가시킨다. 이제 여기에 100만을 곱해보면 리셋이 디자인의 전력 및 면적 증가에 얼마나 커다란 영향을 미치는 지 알 수 있다. 이는 저전력 디자인의 경우 잉여 리셋을 찾아내 제거해야 할 중요한 이유가 된다.

수작업적 기법

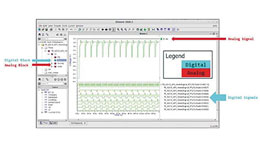

잉여 리셋을 찾아내기 위한 일반적인 방법은 시뮬레이션을 이용해 다음의 작업들을 수행하는 것이다.

1. 레지스터에 리셋 값을 강제한다.

2. 이 레지스터 팬아웃에서 콘스탄스한 전파(propagation)를 수행한다.

3. 잉여(Redundant)동작 구간에 있는 레지스터를 찾아낸다.

하지만 이 기법을 위해서는 레지스터를 수 차례 치환해야 하므로 시간이 매우 많이 걸린다. 또 다른 접근 방법은 다음과 같이 X 전파(X-propagation)를 이용하는 것이다.

1. 리셋을 레지스터로부터 반복적으로 제거한다.

2. X 전파 기법을 이용해 디자인의 기능성을 보장한다.

X 전파 기법에서 리셋이 없는 레지스터들은 초기화 되지 않은 상태 X에 있다. 디자이너는 시뮬레이션을 이용해 X가 최종(Primary) 출력에 도달할 수 있는지 여부를 평가한다. X가 출력에 도달할 수 없다면 해당 리셋은 잉여적인 것이다. 하지만 이 기법은 실행시간이 길다는 단점이 있고, 레지스터가 수백만 개 탑재된 SoC에서는 실용적이 못 된다...(중략)

아날로그 설계를 위한 EDA 툴은 어떻게 진화하고 있는가?

조회수 808회 / Siemens EDA

전자제품 인터페이스의 설계 라이프사이클

조회수 598회 / David Wiens

전기 디자인 룰 체크(DRC)를 자동화하는 방법

조회수 1253회 /

지멘스EDA 수석부사장.jpg)

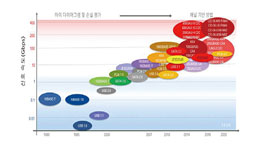

2022년 시스템 및 설계 툴, 방법론의 시장 전망

조회수 1247회 / 지멘스

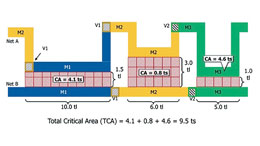

임계 영역을 이용한 자동차 IC의 테스트 품질 향상

조회수 1682회 / RON PRESS

SERDES 디자인을 위한 더 효율적인 솔루션이 있을까요?

조회수 1752회 / Neil Fernandes

지멘스 EDA 포럼 2021 열려, ‘Silicon to Systems’ 주제로 최신 설계 방...

조회수 1149회 / Joseph Sawicki

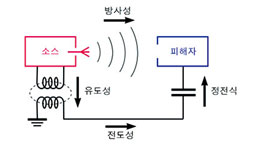

자동화된 EMC 분석을 PCB 레이아웃에 추가

조회수 1229회 / SIEMENS

DFT를 향한 성능 저하 없는 상향식 접근방식

조회수 2548회 / Geir Eide

PDF 다운로드

회원 정보 수정