GaN 신뢰성 및 수명 예측: 15단계(2)

글/Ricardo Garcia, Siddhesh Gajare, Ph.D., Angel Espinoza, Max Zafrani, Alejandro Pozo, Ph.D., Shengke Zhang, Ph.D., EPC

SOA(safe operating area) 테스트는 GaN 트랜지스터를 특정한 펄스 지속시간으로 높은 전류(ID)와 높은 전압(VDS)에 노출시킨다. 이 테스트의 목적은, 트랜지스터가 데이터시트에서 표기하고 있는 SOA 이내의 모든 지점들(ID, VDS)로 결함을 일으키지 않고 동작하는지 확인하는 것이다. 안전 영역 바깥에서 결함을 일으키는 것을 테스트해서 안전 마진을 확인할 수도 있다. SOA 테스트를 실시할 때 다이 상으로 높은 전력 소산으로 인해서 접합부 온도가 급격하게 상승하고 가파른 열 구배(thermal gradient)가 형성된다. 충분히 높은 전력 또는 펄스 지속시간이 가해지면 디바이스가 빠르게 과열되고 심각한 결함을 나타낸다.

이것을 열 과부하 결함이라고 한다. Si MOSFET으로는 SOA 테스트 시에 이차 항복(Spirito 효과라고도 함[2])이라고 하는 또 다른 결함 메커니즘이 관찰된다. 이 결함 모드는 높은 VD에다 낮은 ID일 때 발생되는 것으로서, 접합부 온도와 임계값 VTH 사이의 불안정한 피드백으로 인해서 발생된다. 펄스 동안에 접합부 온도가 상승함에 따라서 VTH가 낮아지는데, 이것은 펄스 전류를 상승하게 만든다. 이렇게 상승하는 전류는 온도가 더 빠르게 상승하도록 만들고, 그럼으로써 양의 피드백 루프를 형성함으로써 열 폭주를 일으키고 결국에 결함으로 이어진다. 이 시험의 목적은 GaN 트랜지스터로 Spirito 효과가 존재하는지 알아보는 것이다.

DC나 지속시간이 긴 펄스로 트랜지스터의 SOA 능력은 디바이스 히트싱크를 어떻게 하느냐에 따라서 크게 좌우된다. 진정한 SOA 능력을 평가하기란 기술적으로 매우 까다로운 일이며, 흔히 특수한 수냉각 히트싱크를 필요로 한다. 하지만 짧은 펄스(1ms 미만)로는 히트싱크가 SOA 성능에 영향을 미치지 않는다. 이처럼 짧은 시간에는 접합부로 발생된 열이 어떠한 외부적 히트싱크로 확산될 수 있는 시간이 충분하지 않기 때문이다. 다만 모든 전기 전력이 변환되면서 GaN 박막과 인접 실리콘 서브스트레이트의 온도(열 커패시턴스)를 상승시킨다. 이러한 점들을 고려해서 이 시험에서는 1ms와 100µs의 두 가지 펄스 지속시간으로 SOA 테스트를 실시했다.

그림 8은 200V EPC2034C의 SOA 데이터를 보여준다. 이 플롯으로 개별 펄스 테스트들을 공간(ID, VDS) 상의 점들로 나타내고 있다. 이 점들을 데이터시트 SOA 그래프와 겹쳐서 보여주고 있다. 100µs 펄스와 1ms 펄스 데이터를 함께 볼 수 있다. 녹색 동그라미는 100µs 펄스로 테스트를 통과한 것이고, 빨간색 동그라미는 테스트에 실패한 것이다. 낮은 VDS에서부터 VDSmax(200V)에 이르기까지 넓은 SOA 영역에 걸쳐서 어떠한 결함을 나타내지 않는다는 것을 알 수 있다(이 영역에 걸쳐서 모두 녹색 동그라미). 모든 결함(빨간색 동그라미)은 (데이터시트 그래프 상의 녹색 선으로 표시된) SOA 영역 바깥에서 발생되고 있다. 1ms 펄스 데이터도 마찬가지다(보라색 및 빨간색 삼각형). 모든 결함은 데이터시트 SOA 영역 바깥에서 발생되고 있다.

그림 9에서는 또 다른 3개 제품으로서 AEC EPC2212(4세대 차량용 100V), EPC2045(5세대 100V), EPC2014C(4세대 40V)의 SOA 데이터를 보여준다. 세 경우 모두로 데이터시트 SOA 영역으로는 결함이 발생되지 않고, 모든 결함은 SOA 한계선 바깥에서 발생되고 있으며 대개가 한계선 훨씬 바깥에서 발생되고 있다는 것을 알 수 있다.

이 데이터시트 SOA 그래프는 디바이스 열 모델(모든 관련 레이어들과 각기 레이어의 열 전도도 및 열 용량 포함)을 사용해서 유한 요소 분석을 통해서 생성된 것이다. 트랜션트 시뮬레이션을 바탕으로 다음과 같은 간단한 기준에 따라서 SOA 한계선을 계산한다. 즉, 주어진 펄스 지속시간으로 펄스가 끝날 때까지 접합부 온도가 150℃를 넘지 않도록 하는 전력 소산이다. 이 기준에 따라서 일정한 전력으로 제한된다. SOA 그래프 상으로 45° 녹색(100µs) 및 보라색(1ms) 선들이 여기에 해당된다.

이 접근법으로 얻어지는 데이터시트 그래프는 안전 동작 영역을 보수적으로 정의한다. 이것은 이 글에서 제시하는 포괄적인 테스트 데이터로도 확인할 수 있다. 전력 MOSFET으로 이와 같은 일정 전력 접근법은 고전압 구간에서 능력을 과대평가하게 된다. 이 구간에서는 열 불안정성으로 인해서 성급하게 결함이 발생된다(Spirito 효과).

결함의 정확한 물리적 성격에 대해서는 좀더 규명할 필요가 있을 것인데, 이 시험에서 확실히 알 수 있는 것은 GaN 트랜지스터가 자신의 데이터시트 SOA 이내로 동작했을 때 결함을 발생시키지 않는다는 것이다.

단락 회로 견고성 테스트

단락 회로 견고성은 FET이 ON(전도) 상태에서 전원 컨버터로 발생되는 예기치 않은 결함 조건을 견디는 능력을 말한다. 이러한 이벤트 시에 디바이스는 최대 버스 전압에다 트랜지스터 고유의 포화 전류와 회로 기생 저항에 의해서만 제한되는 전류를 겪는다. 이 회로 기생 저항은 애플리케이션에 따라서 그리고 결함의 위치에 따라서 달라진다. 보호 회로가 작동해서 이 단락 회로 상태를 진압하지 않는다면 과도한 전력 소산이 결국에 트랜지스터의 열 결함으로 이어질 것이다. 단락 회로 테스트의 목적은 이러한 조건이 발생되었을 때 디바이스가 견디는 시간을 수치화하는 것이다.

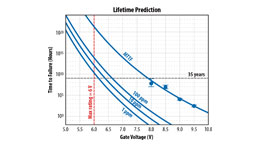

통상적인 보호 회로(예를 들어서 IGBT 게이트 드라이버의 탈포화 보호)는 2~3µs에 과전류 조건을 감지하고 대응할 수 있다. 그러므로 GaN 트랜지스터가 억제되지 않은 단락 회로 조건을 약 5µs 혹은 그 이상 동안 견딜 수 있으면 바람직할 것이다.

참고문헌 [8]에서는 단락 회로 견고성 평가에 주로 사용되는 두 가지 테스트 회로에 대해서 설명하고 있다. 이들 테스트 회로는 다음과 같다:

• HSF(hard-switched fault): 드레인 전압을 인가하고서 게이트를 온으로 (및 오프로) 스위칭한다.

• FUL(fault under load): 게이트가 온인 상태에서 드레인 전압을 온으로 스위칭한다.

이 시험은 디바이스들을 이 두 가지 결함 모드 모두로 테스트했는데, 견딤 시간에 있어서 큰 차이를 발견하지 못했다. 그러므로 이 글에서는 FUL 결과를 위주로 설명하겠다.

다만 HSF 테스트와 관련해서 한 가지 언급하자면, GaN 트랜지스터는 실리콘 기반 IGBT[9]로 발생될 수 있는 것과 같은 어떠한 래칭이나 게이트 제어 소실을 나타내지 않았다. 이것은 GaN 디바이스로 기생 바이폴라 구조를 사용하지 않기 때문인 것으로 짐작된다. 트랜지스터가 심각한 결함을 나타내기 전에 게이트를 로우(low)로 스위칭해서 단락 회로를 완전히 진압할 수 있다. 이것은 보호 회로 디자인을 위해서 이로운 점이다.

다음의 두 가지 GaN 트랜지스터들을 대표로 테스트했다:

1) EPC2203(80V): 4세대 차량용(AEC) 디바이스

2) EPC2051(100V): 5세대 디바이스

이들 디바이스를 선택한 것은 각자 제품군으로 크기가 가장 작은 제품들이기 때문이다. 이들 디바이스는 단락 회로 평가에 필요로 하는 높은 전류가 가능하므로 테스트를 간소화할 수 있다. 그런데 간단한 열 스케일링 인자(thermal scaling argument)에 기반해서, 견딤 시간은 같은 제품군 내의 다른 디바이스들과 동일할 것으로 짐작된다. 그러므로 EPC2203의 결과는 EPC2202, EPC2206, EPC2201, EPC2212에도 해당되며, EPC2051의 결과는 EPC2045와 EPC2053에도 해당된다.

그림 10에서는 일련의 증가하는 드레인 전압으로 EPC2203의 FUL 데이터를 보여준다. VGS 6V와 10µs 드레인 펄스로 60V VDS에 이르기까지는 결함이 발생되지 않는다. 이 조건으로 0.9mm x 0.9mm 다이로 1.5kW 이상을 소산한다. 더 높은 VDS로는 펄스 동안에 시간이 경과하면서 전류가 감소하는 것으로 나타난다. 이것은 디바이스 내에서 접합부 온도가 상승한 결과로서 어떠한 영구적인 저하를 나타내는 것은 아니다.

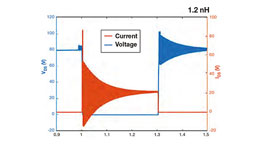

더 긴 펄스 지속시간(25µs)을 사용하면 열 과부하로 인해서 결국에 결함이 발생된다. 그림 11은 이 파형들을 보여준다. 드레인 전류가 갑자기 급격하게 상승하는 것이 결함이 발생되는 때이다. 이 이벤트가 발생되고 나서는 디바이스가 영구적으로 손상된다. 펄스가 시작된 시점부터 결함이 발생된 시점까지가 견딤 시간이다.

견딤 시간에 관한 통계를 얻기 위해서 이 접근법을 사용해서 이들 제품을 8개씩 결함이 발생될 때까지 테스트했다. 표 2는 이 결과를 요약해서 보여준다. EPC2203을 5V(권장 게이트 구동)와 6V(VGS(max))로 테스트했을 때 평균 견딤 시간은 각각 20µs와 13µs이었다. 6V로 견디는 시간이 더 짧은 것은 포화 전류가 더 높기 때문이다. EPC2051은 6V로 EPC2203과 비교해서 결함이 발생되기까지 시간(time-to-fail)이 약간 더 짧다(9.3µs). 이것은 5세대 제품이 좀더 공격적으로 크기를 축소하고 전류 밀도가 높기 때문인 것으로 보인다. 그렇더라도 모든 경우로, 대부분의 단락 회로 보호 회로가 대응해서 디바이스 결함을 방지하기에 별 무리 없이 견딤 시간이 충분이 길다. 뿐만 아니라 견딤 시간이 부품-대-부품으로 차이가 그렇게 크지 않다. 표 2의 하단에서는 펄스 전력과 다이 크기와 관련한 면적당 에너지를 볼 수 있다. 이러한 수치들과 결함이 발생되기까지 시간 사이의 상관관계에 관한 통찰을 얻기 위해서, 시간 종속적 열 전달을 시뮬레이션해서 단락 회로 펄스 동안에 접합부 온도 ΔTJ가 어떻게 상승하는지 알아보았다. 그림 12는 이 결과를 보여준다.

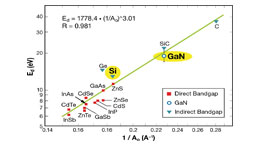

펄스 동안에 강한 전력 밀도는 GaN 레이어와 인근 실리콘 서브스트레이트로 급격하게 열을 발생시킨다. 그런데 펄스는 짧고 열 전달은 상대적으로 느리므로 반도체의 적은 두께(깊이에 있어서 100µm 이내)만이 에너지를 흡수한다. 온도는 시간의 제곱근으로 상승하고(열 확산의 특성) 펄스 전력에 따라서 선형적으로 상승한다. 그림 12에서 보듯이, EPC2203으로 5V와 6V 조건 모두 ~475℃의 동일한 접합부 온도 상승에 결함을 일으킨다. EPC2051도 마찬가지여서, 두 조건 모두 ~575℃의 동일한 ΔTJ에 결함을 일으킨다. 이러한 결과로부터 다음과 같은 세 가지 결론을 도출할 수 있다:

1) 특정 디바이스로 결함이 발생되기까지 시간은 전력 소산의 제곱에 반비례한다(P-2). 이것은 1ms 미만의 단락 회로 및 SOA 펄스일 때 그렇다.

2) 고전력 펄스로 인한 내인성 결함 모드는 접합부 온도가 특정한 임계 값을 초과하는 것과 직접적으로 연관이 있다.

3) 와이드 밴드갭 eGaN 디바이스는, 실리콘 디바이스로는 자유 캐리어 열 폭주 때문에 절대로 불가능한 접합부 온도(400℃ 이상)를 견딜 수 있다.

디바이스들이 반복적으로 이와 같은 극단적인 조건을 견딜 수 있는지 알아보기 위해서, 다수의 부품들로 디바이스 전류가 데이터시트 상에 표기된 최대 정격 펄스 전류의 두 배가 되도록 하는 단락 회로 조건으로 500,000회 이상의 사이클을 가했다. 이 테스트 셋업으로 테스트 대상 디바이스(DUT)의 게이트로 5VDC 또는 6VDC 게이트 바이어스를 인가했다. 드레인 바이어스는 10VDC로 설정하고, 드레인 전원으로 60mF 커패시터를 연결했다. DUT와 직렬로 RDS(on)이 낮은 상측 트랜지스터를 사용해서(그러지 않는다면 제한되지 않을) 전류 플로우를 제어했다. 그런 다음 이 제어 트랜지스터를 1Hz로 5µs 펄스를 사용해서 펄싱해서 채널이 다시 평형을 이룰 수 있는 시간을 주었다. 표 3은 이렇게 테스트한 디바이스들과 이들 디바이스의 데이터시트 최대 펄스 전류 정격과 각기 사이클 동안에 디바이스를 통해서 펄싱한 단락 회로 전류 양을 보여준다.

[표 4] 펄스 테스트를 시작할 때, 100k 펄스 후에, 500k 펄스 후에, 175℃로 10분 동안 식힌 후에 EPC2051의 주요 파라미터. 디바이스 파라미터들이 모든 시간에 데이터시트 한계 이내로 유지되는 것으로 나타난다.

기계적 스트레스

어떤 제품의 최종 수명이나 특정 애플리케이션으로 적합성은 얼마만큼의 스트레스를 겪느냐에 따라서 제한될 수 있다. 이 장에서는 대표적인 기계적 스트레스 요인으로서 다이 전단, 후면 압력, 굽힘 힘에 대해서 알아보고, WLSCP 패키지가 통상의 어셈블리 또는 탑재 조건으로 견고하다는 것을 설명한다.

(1) 다이 전단(die shear) 테스트

다이 전단 테스트의 목적은 eGaN 디바이스를 PCB로 접착하기 위해서 사용된 솔더 접합부의 무결성을 평가하기 위한 것이다. 이 평가는 탑재된 디바이스로 힘을 가해서 다이가 PCB로부터 전단될 때의 평면내 힘(in-plane force)을 기준으로 한다. 모든 테스트는 군용 테스트 표준인 MIL-STD-883E, Method 2019[12]에 따라서 실시했다. 그림 13은 선택한 4개 GaN 트랜지스터의 테스트 결과를 보여준다. 각기 제품을 10개씩 테스트했다. 다이 크기가 가장 작은 디바이스는 EPC2036/EPC2203으로서, 직경 200µm인 4개 솔더 볼만을 포함하며 다이 면적은 0.81mm2이다. 예상대로 이 제품이 전단 강도가 가장 낮은 것으로 드러났다(그림 13). 그렇더라도 MIL 표준에서 정한 최소 힘 요건을 상회해서 충족한다. 다이가 가장 큰 제품은 EPC2206으로서, LGA(land grid array) 제품이고 다이 면적은 13.94mm2이다. EPC2206은 최소 힘 요건을 10배 이상 상회해서 충족한다. 이 크기 스펙트럼 상에서 추가적인 두 제품도 테스트했다. EPC2212(100V LGA)와 EPC2034C(200V BGA)이다. 두 제품 모두 최소 힘 요건을 훨씬 상회했다. 그림 13의 결과를 보면, 모든 WLCSP GaN 제품이 극히 엄격한 조건으로 환경적 전단 스트레스에 대해서 기계적으로 견고하다는 것을 알 수 있다.

(2) 후면 압력(backside pressure) 테스트

GaN 디바이스의 기계적 견고성에 있어서 또 다른 중요한 측면은 후면 압력을 얼마나 잘 처리하느냐 하는 것이다. 이것은 다이로 후면 히트싱크를 필요로 하는 애플리케이션으로 특히 중요하다. 이 테스트는 어셈블리 시에 안전한 ‘픽 앤 플레이스’ 탑재 힘을 결정하기 위해서도 중요하다.

최대 400psi로 후면 압력 테스트를 실시했다. 여기서 압력은 가해진 힘을 다이 면적으로 나눈 것이다. 분당 0.6mm의 로딩 속도를 사용해서 다이 후면으로 곧바로 압력을 가했다. 압력 테스트 전과 후에 파라메트릭 테스트를 실시해서 합격 또는 불합격을 판단했다. 후속적으로 60VDS, 85℃, 85% 상대 습도로 300시간 동안 습도 바이어스 테스트(H3TRB)에 노출시켰다. H3TRB는 압력 테스트 시에 기계적 손상으로 인한 어떠한 잠재적 결함(내부적 균열)이 발생되었는지 확인하기 위해서 효과적이다.

EPC2212(100V LGA)와 EPC2034C(200V BGA)를 테스트했는데, 둘 다 400psi를 통과했다. 이 데이터는 표 5에 포함되어 있다. 이 결과를 보면, eGaN FET이 PCB 어셈블리 업체들에서 통상적으로 사용하는 후면 압력을 취급하기에 여유가 충분하다는 것을 알 수 있다. 이들 제품이 400psi를 충분히 취급하기는 하지만, EPC는 최대 후면 압력을 50psi 혹은 그 이하로 제한할 것을 권장한다.

[표 5] eGaN 디바이스의 압력 테스트 결과

(3) 굽힘 힘(bending force) 테스트

굽힘 힘 테스트의 목적은 GaN 트랜지스터가 PCB 취급, 어셈블리, 가동 시에 발생될 수 있는 PCB 휘어짐을 견디는 능력을 평가하기 위한 것이다. 이 테스트 규격은 수동 표면실장 부품들을 위해서 개발된 것인데(AEC-Q200)[13], 많은 고객들이 다음과 같은 두 가지 이유에서 GaN 트랜지스터의 굽힘 힘에 대해서 염려를 나타내고는 한다:

1. WLCSP 솔더 접합부의 견고성

2. 트랜지스터 내의 압전 효과가 디바이스 파라메트릭 값을 변화시키고 회로 동작을 방해할 수 있다는 점

이러한 염려를 불식하기 위해서 AEC-Q200-005A 테스트 표준[14]에 따라서 4개 EPC2206 디바이스에 대해서 굽힘 힘 테스트를 실시했다. FR4 PCB(100mm 가로 x 40mm 세로 x 1.6mm 두께)의 중심 부근으로 디바이스들을 탑재했다. 양쪽을 단단히 고정시키고 디바이스 반대편으로 힘을 가해서 PCB가 위를 향해서 휘어지도록 했다. 이렇게 휘어진 상태로 60초가 지난 후에 디바이스의 모든 전기적 파라미터들을 측정했다.

표 6은 이렇게 테스트한 4개 디바이스로 보드 휘어짐에 따른 정규화 RDS(on)을 보여준다. 모든 디바이스가 2mm 테스트 요건을 통과하고 있다. 두 디바이스는 6mm 휘어짐에서 결함을 일으키고, 나머지 둘은 8mm에 이르기까지 살아남는 것으로 나타난다. 사후 해부 검사에서 결함 모드는 솔더 접합부 균열이 발생되고 이것이 게이트 배선 개방으로 이어진 것으로 나타났다. 결함이 발생될 때까지는 RDS(on)이 보드 휘어짐에 대해서 어떠한 눈에 띄는 반응을 나타내지 않았다. VTH나 IDSS 같은 다른 전기적 특성들도 마찬가지로 관찰되었다.

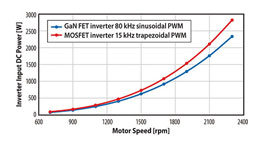

모터 인버터에서 GaN 전력 소자를 사용하는 방법

조회수 166회 / EPC

5세대에 이르기까지의 개발 여정

조회수 132회 / Alex Lidow

EPC의 5세대 eGaN® 기술 “새로운 차원의 성능으로 비약적 도약”

조회수 152회 / Alex Lidow

GaN FET에 실리콘 MOSFET 게이트 드라이버를 사용하기 위한 방법

조회수 323회 / Alejandro Pozo

최고의 GaN 게이트 드라이버 선택

조회수 297회 / 류창우

GaN 모터 구동 인버터를 활용한 농업용 드론 혁신

조회수 350회 / EPC

GaN 신뢰성 및 수명 예측: 15단계(8)

DC-DC 컨버터(Ⅱ)

조회수 349회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(7)

DC-DC 컨버터(I)

조회수 387회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(6)

“test-to-fail” 방법론을 사용...

조회수 565회 / Ricardo Garcia 외 5인

PDF 다운로드

회원 정보 수정