칩 스케일 패키지 GaN FET으로 PCB 전원 루프 레이아웃을 통한 열 성능 최적화

글/Assaad Helou and John Glaser, Senior Applications Engineer, Efficient Power Conversion(EPC Corporation)

머리말

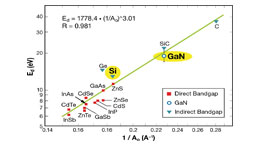

갈륨 나이트라이드(GaN) 같은 와이드 밴드갭(WBG) 전력 반도체는 동급의 실리콘 디바이스와 비교해서 3~10배의 FOM(figure of merit)으로 더 우수한 스위칭 성능, 신뢰성, 열 성능을 달성하는 것으로 입증되고 있다[1]. GaN 디바이스는 작은 크기와 낮은 온 저항(RDS,on)으로 기생 커패시턴스와 인덕턴스를 낮추고, 스위칭 속도를 높이고, 스위칭 손실을 낮춤으로써 훨씬 더 높은 전력 밀도와 효율을 가능하게 한다. 그런데 높은 주파수로 동작하므로 열 저항과 인덕턴스가 높아지는 것을 최소화하기 위해서 설계 시에 레이아웃을 잘 해야 한다[2].

이 글에서는 각기 다른 전원 루프 레이아웃을 분석하고 열 관리와 전기적 기생성분을 살펴본다. 레이아웃을 향상시킴으로써 온도가 상승되는 것을 크게 줄이면서 전기적 성능 이점은 그대로 유지할 수 있다는 것을 알 수 있다.

기존의 PCB 레이아웃 접근법

이 글에서는 대다수 전원 변환에 흔히 사용되는 하프 브리지 구성을 예로 들어서 전원 루프 레이아웃을 설명한다. 그림 1에서 보듯이 하프 브리지 구성은 2개 전력 반도체 스위치와 하나의 바이패스 커패시터를 포함한다. 인덕터(L)가 스위치 노드 vSW = VLOW의 출력 전압 레벨을 애버리징하고, 커패시터 CHF는 VHIGH와 병렬이므로 이론적으로는 필요하지 않은데 실제적으로 고주파 전류를 위한 저 임피던스 경로를 제공하기 위해서 필요하다.

지난 글에서는 Lloop = µ0·l·t/w의 계산식에 따라서 PCB 디자인으로 전원 루프 인덕턴스를 최소화할 수 있다는 것을 설명했다[2]. 그림 1은 PCB 전원 루프 구현을 보여준다. PCB 레이아웃을 설계할 때 길이 l과 두께 t는 최소화하고 폭 w는 늘리도록 해야 한다. 그렇게 한 것이 그림 1c와 같은 레이아웃이다. l과 w는 부품들의 물리적 치수에 따라서 결정되며, t는 전압 요구나 PCB 제조 상의 제약에 따라서 결정된다.

[그림 1] 통상적인 하프 브리지 빌딩 블록. 병렬 판 단락 트랜스미션 라인(a), 저 임피던스 트랜스미션 라인을 전원 루프 구조로 사용하는 하프 브리지 레이아웃(b)과 이 레이아웃의 측면 모습(c)

[그림 2] 위는 전원 루프 레이아웃을 확대한 모습으로서, 레퍼런스 노드와 리턴 경로(GND)를 녹색으로 표시하고 있다. 아래는 이들 레이아웃의 상단면 모습으로서, 열 흐름 경로를 화살표로 표시하고 있다.

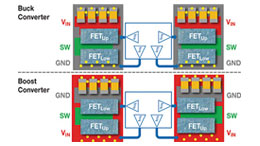

기존 레이아웃으로 벅 컨버터의 열 과제

많은 애플리케이션으로 스위칭 디바이스 온도가 전기적 동작에 있어서 제한 요소가 됨으로써, PCB 차원에서 열 소산을 향상시키는 것이 중요한 설계 과제가 되었다. 이 설계가 FET으로부터 열을 빼내기 위해서 중요한 역할을 한다[3]. 그림 1의 벅 컨버터로는 Q1이 열 부하가 더 높다. 스위칭 손실과 전도 손실을 모두 나타내기 때문이다. Q2는 전도 손실만을 나타낸다. 그림 2의 레이아웃 A는 그림 1(c)의 표준 레이아웃을 확대한 모습이다. 열적으로 상단면에서 Q1의 경로로 저항이 더 높다. CHF로 인해서 구리 플레인이 가로막히기 때문이다. 반면에 Q2로는 구리 플레인이 트여 있으므로 열이 효과적으로 PCB로 확산되고 마침내 주변으로 소산된다. 더욱이 Q1으로는 이용할 수 있는 비아가 더 적다. 이것은 GND 리턴 경로로 집중적으로 구멍을 내는 것을 피하기 위해서다. 그러므로 레이아웃 A는 열적으로 벅 컨버터 애플리케이션에 적합하지 않으며, Q1으로 과열을 일으키지 않으면서 손실을 더 잘 수용할 수 있도록 향상된 레이아웃이 필요하다.

부스트 컨버터 애플리케이션으로는 Q1과 Q2의 역할이 반대가 되고 Q2로 손실이 더 높다. 이 경우에는 레이아웃 A가 Q2로 열 저항이 더 낮기 때문에 더 잘 맞는다.

벅 컨버터로 레이아웃 최적화

벅 동작으로 레이아웃 A를 열적으로 향상시키기 위해서 CHF를 Q2 옆으로 옮길 수 있다(그림 2의 레이아웃 B). 둘 다 GND로 연결되기 때문이다. 그러기 위해서는 레이어 2를 VHIGH 플레인으로 사용해야 한다. 그렇더라도 여전히 AC 레퍼런스 플레인으로서 동작하며, l, w, t는 변화되지 않는다. 그러면 이제 열적으로 Q1 경로가 주변으로 잘 소산한다. 그러므로 레이아웃 B는 열적으로 벅 동작에 잘 맞으며 부스트 동작으로 사용하기에는 나쁘다. Q2가 CHF에 의해서 가로막히기 때문이다.

커패시터를 가운데에 배치하는 레이아웃

넓은 컨버터 동작 범위나 양방향 변환(벅과 부스트 모두)을 필요로 하는 경우에 레이아웃 A나 B는 열적으로 어느 한 FET으로 치우칠 수 있다. 뿐만 아니라 두 레이아웃 모두 Q1과 Q2가 가깝게 배치됨으로써 발생된 열이 좁은 영역으로 집중될 수 있다. 레이아웃 C는 CHF를 Q1과 Q2 사이에 배치함으로써 이러한 문제들을 피할 수 있다. 레이아웃 C는 그림 2에서 보듯이 레이어 2로 스위치 노드(SW)를 통해서 Q1과 Q2를 연결한다. 레이아웃 C는 루프 인덕턴스를 최소화하기 위한 원칙을 따르고 있다. 스위치와 신호 노드를 바깥쪽 레이어에 배치하는 것이 통상적이기는 하나, 낮은 임피던스를 달성하고자 할 때는 꼭 그러지 않을 수도 있다. 두 노드 VHIGH와 VLOW가 CHF에 의해서 동일한 AC 전위이고, 그러므로 둘이 AC 레퍼런스 플레인을 형성하고 루프 인덕턴스에 영향을 미치지 않는다.

레이아웃 C는 Q1과 Q2 사이에 간격을 띄우고 둘 다로 구리 플레인이 장애물에 가로막히지 않으므로 열적으로 유리하다. 또한 인접한 비아들로 더 많은 공간을 할애하고, 리턴 플레인으로 구멍을 줄이고, 스위치 노드를 DC 플레인으로 차폐할 수 있다. 이 점은 EMI 측면에서 유리하다.

대수롭지는 않지만 몇 가지 단점이라면, FET들 사이에 간격이 늘어남으로써 단일 패키지 게이트 구동 IC를 사용할 때 더 긴 게이트 구동 경로가 필요할 수 있고, 또 경우에 따라서는 커패시터가 FET보다 높이가 더 높을 수 있으므로 히트싱크를 탑재하고자 할 때 이 점을 고려해야 한다.

분석과 검증

위의 설계 제안을 검증하기 위해서 하드 스위칭 컨버터를 사용해서 테스트를 실시했다. 하드 스위칭 컨버터는 설계하기가 쉽고 동작이 잘 알려져 있다는 것이 장점이다. 벅 및 부스트 동작으로 3개 레이아웃 디자인의 열 성능을 비교했다. 각기 전원 루프 레이아웃을 사용해서 동일한 보드를 설계하고 제작했다. VHIGH 전압은 Q1과 Q2에 사용된 FET들로 통상적인 값으로서 150V를 선택했다. 변환 비율은 VLOW/VHIGH = 0.25로 고정적이다. 다시 말해서 Q1은 0.25의 듀티 사이클로 동작하고, Q2는 0.75의 듀티 사이클로 동작한다. dc 인덕터 전류는 IL = 15A로 고정적이다. 이 값은 인덕터 포화 값에 가깝고 채택한 FET들로 통상적인 값이다. 이러한 테스트 파라미터를 사용해서 테스트를 실시했다. 그러므로 이 컨버터는 모든 테스트 사례로 562W를 처리한다. 스위칭 주파수는 FSW = 100kHz로 선택했다. 벅 모드로는 Q1이 열적으로 과도한 스트레스를 받고, 부스트 모드로는 Q2가 열적으로 과도한 스트레스를 받는다.

시뮬레이션과 측정

FET들로 열 소산을 구하기 위해서 LTspice™로 전기적 시뮬레이션을 실시했다. 여기에는 PCB 기생성분 계산도 포함했다. 주파수, 듀티 사이클, 온도에 대한 함수로서 FET 손실을 시뮬레이션했다. 그림 3a는 이 결과를 보여준다.

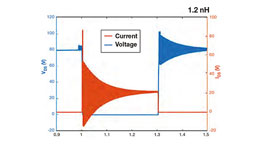

또한 각기 다른 레이아웃으로 인덕턴스 차이를 알아보기 위해서 스위칭 성능을 측정했다. 그림 3b의 스위칭 파형은 벅 동작으로 Q1 턴온 시의 스위칭 노드 전압을 보여준다. 3개 레이아웃이 링잉에 있어서 약간의 차이를 나타낸다는 것을 알 수 있다. 이것은 기생 인덕턴스로 약간의 영향을 미친다는 것을 시사한다.

[그림 3] a) 손실 시뮬레이션 결과, b) 벅 컨버터 Q1 턴온 전이 시에 스위치 노드 전압 VSW

열 테스트 셋업

강제 공기 냉각 테스트 체임버에서 통제된 에어플로우를 사용해서 열 테스트를 실시했다. 그림 4는 테스트를 위한 연결과 시험 셋업을 보여준다. 열 측정을 위해서 패드들 사이에 PCB로 200µm 폭의 구멍을 뚫어서 광학 열 센서(OPSense® OTG-F 센서)를 연결했다. 이 센서는 EMI 내성이 우수하고 열 질량이 극히 작다.

[그림 4] a) 열 테스트를 위한 마더보드와 테스트 PCB의 전기적 연결, b) 광학적 센서 측정 셋업을 보여주는 것으로서, PCB로 구멍을 내서 광섬유 센서를 연결했다.

열 시뮬레이션 모델

측정을 검증하기 위해서 상업용 열 및 CFD 소프트웨어로서 6SigmaET를 사용해서 열 시뮬레이션을 실시했다[4]. 이 소프트웨어로 필요한 모든 세부사항(구리 도체, 비아, 디바이스)과 함께 PCB 레이아웃을 불러왔다. 데이터 포인트들을 사용해서 측정을 검증했다.

[그림 5] 부스트 동작으로 레이아웃 C의 측정 결과(IR 및 광섬유 온도 센서)와 시뮬레이션 결과(표면 온도)

강제 공기 대류 결과

먼저 3개 레이아웃으로 400 LFM 에어플로우를 사용해서 측정을 실시했다. 그림 3에서 벅 및 부스트 구성으로 열 시뮬레이션 결과로부터 상측 FET의 최대 온도를 보면 부스트로는 레이아웃 A가 열적으로 유리하고 벅 모드로는 레이아웃 B가 열을 소산시키기에 더 효과적이라는 것을 알 수 있다.

레이아웃 C를 A 및 B와 비교해 보면, 각자 최적 동작 모드(부스트 모드로 A 및 벅 모드로 B)로 A 및 B와 비교해서는 열 성능이 비슷하거나(5% 이내) 더 우수하고, 최적이 아닌 동작 모드(벅 모드로 A 및 부스트 모드로 B)로 A 및 B와 비교해서는 성능이 훨씬 더 우수하다는 것을 확인할 수 있다. 그림 6은 벅과 부스트 동작으로 3개 레이아웃으로 측정된 Q1 및 Q2 온도를 보여준다. 이 결과를 보면, 레이아웃 C가 양방향 동작으로 열적으로 결코 불리하지 않다는 것을 알 수 있다. 반면에 레이아웃 A는 벅 모드로 열 성능이 떨어지고(10% 더 높은 온도), 레이아웃 B는 부스트 모드로 열 성능이 떨어진다(25% 더 높은 온도). 히트싱크를 사용한 테스트에서도 마찬가지의 결과를 볼 수 있다. 더 효과적인 냉각에다 레이아웃 C로 Q1과 Q2 사이에 더 넓은 간격에 의해서 온도가 더 낮게 나타난다[5].

[그림 6] 3개 레이아웃으로 측정 결과와 온도 상승 비교

맺음말

3개 레이아웃 A(CHF를 Q1 가까이 배치), B(CHF를 Q2 가까이 배치), C(CHF를 Q1과 Q2 사이에 배치)가 거의 비슷한 전기적 성능을 나타내며 링잉 주파수에 있어서 미미한 차이만이 관찰되었다. 시험을 통해서 레이아웃 A는 열적으로 부스트 컨버터 동작에 적합하고 레이아웃 B는 벅 동작에 적합할 것이라는 가정을 확인할 수 있었다. 레이아웃 A는 벅 동작으로 사용했을 때 열적으로 어려워지고 레이아웃 B는 부스트 동작으로 사용했을 때 열적으로 어려워짐으로써, 각기 적합한 모드가 아닐 때 열적으로 더 불리하다는 것을 알 수 있다(더 높은 피크 온도).

레이아웃 C는 구리 플레인이 장애물에 가로막히지 않고 Q1과 Q2 사이에 간격이 늘어남으로써 레이아웃 A나 B와 최소한 거의 같은 수준이나 혹은 더 우수한 수준으로 전반적인 열 성능을 향상시킨다. 레이아웃 C는 테스트 시에 어떤 중대한 단점들을 나타내지 않음으로써 어느 동작으로도 열적으로 적합하다는 것을 확인할 수 있었다. 레이아웃 C는 인버터, Class D 증폭기, 태양광 최적화기 같은 다양한 애플리케이션에 사용하기에 적합하며 배터리 인터페이스 같은 양방향 애플리케이션에도 사용할 수 있다.

[참고문헌]

[1] A.Lidow, M. De Rooij, J. Strydom, D. Reusch, J. Glaser, “GaN Transistors for Efficient Power Conversion.” Third Edition, Wiley. ISBN 978-1-119-59414-7

[2] D. Reusch and J. Strydom, “Understanding the effect of PCB layout on circuit performance in a high frequency gallium nitride based point of load converter,” in 2013 twenty-eighth annual IEEE applied power electronics conference and exposition(APEC), Mar. 2013, pp. 649?655. doi: 10.1109/APEC.2013.6520279

[3] J. S. Glaser, A. Helou, M. Sharma, R. Strittmatter, and M. de Rooij, “Simple high-performance thermal management of chip-scale GaN FETs,” in 2021 IEEE Applied Power Electronics Conference and Exposition(APEC), Jun. 2021, pp. 44?49. doi: 10.1109/APEC42165.2021.9487121

[4] 6SigmaET. Future Facilities, 2021. [Online]. Available: https://www.6sigmaet.info/

[5] Assaad Helou, “How2AppNote012 - How to Get More Power Out of an eGaN Converter.pdf,” Efficient Power Conversion Corporation, Application note How2AppNote 012, 2021. [Online].

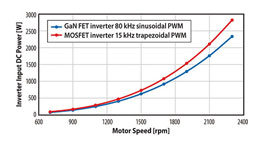

모터 인버터에서 GaN 전력 소자를 사용하는 방법

조회수 166회 / EPC

5세대에 이르기까지의 개발 여정

조회수 132회 / Alex Lidow

EPC의 5세대 eGaN® 기술 “새로운 차원의 성능으로 비약적 도약”

조회수 152회 / Alex Lidow

GaN FET에 실리콘 MOSFET 게이트 드라이버를 사용하기 위한 방법

조회수 323회 / Alejandro Pozo

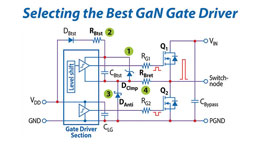

최고의 GaN 게이트 드라이버 선택

조회수 297회 / 류창우

GaN 모터 구동 인버터를 활용한 농업용 드론 혁신

조회수 350회 / EPC

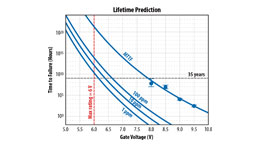

GaN 신뢰성 및 수명 예측: 15단계(8)

DC-DC 컨버터(Ⅱ)

조회수 349회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(7)

DC-DC 컨버터(I)

조회수 387회 / Ricardo Garcia 외 5인

GaN 신뢰성 및 수명 예측: 15단계(6)

“test-to-fail” 방법론을 사용...

조회수 564회 / Ricardo Garcia 외 5인

PDF 다운로드

회원 정보 수정