GaN FET에 실리콘 MOSFET 게이트 드라이버를 사용하기 위한 방법

글/Alejandro Pozo, Ph.D., Efficient Power Conversion

머리말

갈륨 나이트라이드(GaN) FET이 전력 전자 산업을 혁신하고 있다. GaN FET은 전통적인 실리콘 MOSFET과 비교해서 더 작은 크기, 더 빠른 스위칭, 더 높은 효율, 더 낮은 비용이 가능하다. 그런데 GaN 기술이 빠르게 진보하는 것에 비해서 GaN 전용 게이트 드라이버 및 컨트롤러는 더디게 개발되고 있다. 이 때문에 회로 디자이너들이 종종 실리콘 MOSFET 용으로 설계된 범용 게이트 드라이버로 눈을 돌린다. 이러한 경우에 최상의 성능을 달성하기 위해서는 다양한 요소들을 신중하게 고려해야 한다. 이 글에서는 GaN FET과 실리콘 MOSFET이 어떻게 다르고, GaN FET에 범용 게이트 드라이버를 사용할 때 어떤 점들을 고려해야 하고, 하프 브리지 게이트 드라이버 및 컨트롤러로 어떤 변경들이 필요한지 설명한다.

GaN 트랜지스터와 Si MOSFET의 차이점

eGaN® FET은 실리콘 MOSFET과는 다른 특성들을 나타낸다. 그러므로 실리콘 MOSFET 용으로 설계된 게이트 드라이버를 사용하면 GaN FET의 동작에 영향을 미칠 수 있다. 둘 사이에는 다음과 같은 차이점을 들 수 있다:

ⓐ 더 낮은 게이트 전압 수준: EPC의 eGaN FET은 턴온을 위해서 5V 및 턴오프를 위해서 0V의 게이트 전압을 필요로 하고, 최대 게이트 정격은 6V이다. 그러므로 게이트 드라이버를 구동하는 전원장치를 그에 부합하게 설계해야 한다. 드라이버 또는 컨트롤러의 UVLO 역시도 5V 게이트 구동과 일치해야 한다.

ⓑ 더 빠른 스위칭 속도: GaN과 비교해서 Si MOSFET은 RDS(on) · QG는 3배 이상이고 RDS(on) · QGD는 10배까지 더 높다[1]. 결과적으로 GaN은 스위치 노드로 dv/dt가 75V/ns 혹은 그 이상일 수 있다. 그러므로 게이트 드라이버가 그와 같은 슬루율을 견딜 수 있어야 한다. 더 빠른 스위칭 속도는 또한 기생 인덕턴스를 더욱 두드러지게 만든다. 그러므로 인덕턴스를 낮추는 레이아웃 기법이 필요하다.

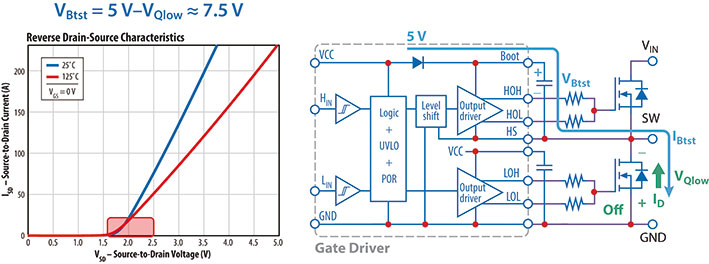

ⓒ 더 높은 역 전도 전압 강하: 실리콘 MOSFET과 달리, eGaN FET은 기생 바디 다이오드를 포함하지 않고 더 높은 전압 강하로 역방향으로 전류를 전도한다. 이 전압 강하가 MOSFET은 1V인데 비해서 최대 2.5V까지 이른다[1]. 그러므로 게이트 드라이버가 데드 타임 시에 정류 스위치로 더 높은 음의 스위치 노드 전압을 겪는다. 그러므로 게이트 드라이버가 부트스트랩 과전압 관리 기능을 포함해야 하며 -5V까지 이르는 음의 스위치 노드 전압으로 동작할 수 있어야 한다.

ⓓ 물리적 구조: eGaN FET은 측방향 구조인데[1], 20V 이상 정격의 Si MOSFET은 통상적으로 수직형 디바이스이다. 그러므로 핀 위치가 다를 수 있고, Si MOSFET 용으로 설계된 게이트 드라이버를 사용할 때 레이아웃을 까다롭게 할 수 있다. GaN 전용 게이트 드라이버는 대부분의 GaN 트랜지스터와 레이아웃 호환이 가능하도록 설계된다. GaN FET에 MOSFET 드라이버를 사용하면서 레이아웃 불일치에 직면했을 때 설계를 어떻게 절충할 것인지 이해해야 한다.

MOSFET 게이트 드라이버 호환성 고려

MOSFET 게이트 드라이버를 사용해서 GaN FET을 구동하도록 설계하기 위해서는 몇 가지 조건이 충족되어야 한다.

① 5V 전원과 호환성: 게이트 드라이버가 드라이버 스테이지의 5V 전원과 호환 가능해야 한다. 레귤레이트된 외부적 전원을 사용하거나 내부적 LDO(low dropout regulator)를 사용할 수 있다.

② UVLO 호환성: 저전압 록아웃(UVLO)이 5V 드라이버 스테이지와 호환 가능해야 한다. 통상적으로 하측 드라이버 스테이지의 UVLO는 3.75V ~ 4V이고, 상측은 3.25V ~ 3.75V이다.

③ 슬루율 내성: 게이트 드라이버가 스위치 노드로 예상되는 최대 dv/dt를 초과하는 슬루율을 견딜 수 있어야 한다. 50kV/μs 이상이면 바람직하다. 이 조건을 만족시킬 수 없으면 스위칭 속도를 낮춰야 하는데, 그러면 컨버터 효율이 감소한다.

④ 부트스트랩 전원장치: 많은 MOSFET 드라이버가 상측 디바이스 드라이버를 구동하기 위해서 부트스트랩 회로를 사용하고 대부분이 부트스트랩 다이오드를 사용한다. GaN FET에는 ‘외부적’ 부트스트랩 다이오드를 사용하는 게이트 드라이버만이 적합하다. 그러므로 부트스트랩 다이오드 후위에 LDO를 포함하는 드라이버가 바람직하다.

⑤ 데드 타임 기능: eGaN FET은 스위칭 특성이 뛰어나므로 MHz 대로 동작하면서 높은 컨버터 효율을 유지할 수 있다. 그러므로 데드 타임을 10ns보다도 낮게 최소화하는 것이 매우 유리하다. MOSFET 용으로 설계된 일부 컨트롤러들은 이와 같이 낮은 수준의 데드 타임이 불가능하다. 그러므로 GaN 디바이스의 이점을 무색하게 한다. GaN FET에 사용할 컨트롤러를 고를 때는 낮은 데드 타임이 가능한 컨트롤러를 우선적으로 선택하도록 한다.

MOSFET 드라이버를 GaN FET에 사용하도록 변경하는 방법

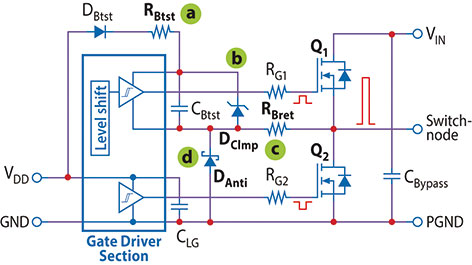

호환 가능한 MOSFET 드라이버를 선택한 다음에는 다음과 같은 방법으로 GaN FET과의 호환성을 극대화할 수 있다. 그림 1은 이에 관해서 설명하고 있다. 다음의 권장사항과 함께 GaN FET 구동에 관한 일반 권장사항[1]을 언제나 따라야 한다.

① 부트스트랩 다이오드: 외부적 부트스트랩 다이오드는 BAT54KFILM[2] 같이 크기, 커패시턴스, 전류 정격이 되도록 작은 쇼트키 다이오드를 사용한다. 그리고 그림 1(a)에서 보듯이 전류 제한 저항과 직렬로 연결한다. 이 쇼트키 다이오드가 전압 손실(Vboot-Vsw)을 최소화하고 그럼으로써 드라이버 전압을 5V에 되도록 근접하게 유지한다. 이 작은 직렬 저항이 어떠한 보호 회로가 작동되었을 때 부트스트랩 다이오드의 전류를 제한한다. 다만 이 저항은 부트스트랩 커패시터를 충전하기 위해서 필요한 최소 펄스 폭에 영향을 미칠 수 있다. 부트스트랩 다이오드 후위에 5V LDO를 포함하는 드라이버는 직렬 저항을 필요로 하지 않으며, 아니면 아래에서 권고하는 것과 같은 추가적인 회로 보호가 선택 사항이 된다.

② 부트스트랩 클램프: 하측 디바이스가 역 전도 상태인 데드 타임 시에 과전압을 방지하기 위해서 부트스트랩 커패시터 상으로 제너 다이오드를 사용해서 전압을 6V 아래로 클램프할 수 있다. 그림 1(b)에서 보는 것과 같이 제너 전압이 5.6V인 MM5Z5V6ST1G[3]가 좋은 예이다. 부트스트랩 커패시터와 제너 다이오드 모두 서로 간에 되도록 가깝고 게이트 드라이버에 되도록 가깝게 배치해야 한다.

③ 게이트 리턴 저항: 상측 FET으로 그림 1(c)와 같은 게이트 리턴 저항을 추가함으로써 그림 2에서 보는 것과 같이 하측 GaN FET의 역 전도 시에 스위치 노드 상으로 높은 음의 전압으로부터 IC를 보호할 수 있다. 이 저항 값은 상측 디바이스 게이트 회로로 필요한 턴오프 댐핑 및 타이밍에 따라서 달라진다. 이 저항을 사용할 때는 게이트 턴온 저항을 그만큼 낮춰서 저항을 보상해야 한다.

④ 역 전도 클램프: 하프 브리지 토폴로지의 하측으로 그림 1(d)와 같은 역 평행 쇼트키 다이오드를 사용해서 드라이버가 겪는 음의 스위치 노드 전압의 크기를 제한할 수 있다. 일부 게이트 드라이버는 스위치 노드가 접지 레퍼런스 아래의 특정한 전압보다 낮게 떨어지는 것에 민감하거나 또는 결함을 일으킬 수 있다[4]. 이 다이오드의 전압 정격은 하측 GaN FET과 일치해야 한다. 전류 정격은 하측 FET보다 훨씬 낮을 수 있다. 하측 FET은 데드 타임 시에만 전도하기 때문이다. 그러므로 펄스형 전류 정격을 기준으로 선택해야 한다.

[그림 2] 데드 타임 시에 부트스트랩 충전 경로

게이트 드라이버를 통합한 컨트롤러 IC 사용

컨트롤러 IC는 단일 IC로 다수의 기능들을 통합할 수 있으며, 게이트 드라이버를 통합할 수도 있다[5-7]. 이러한 일부 IC는 GaN 디바이스에 사용할 때 최적의 레이아웃이 불가능할 수 있다. 그러므로 최상의 성능을 달성하려면 설계 절충을 어떻게 할지 이해해야 한다.

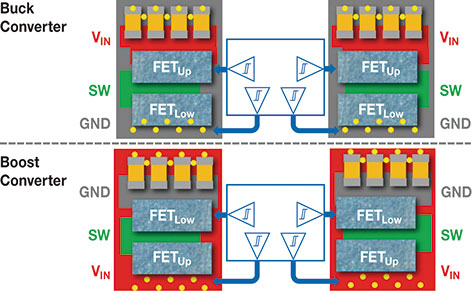

GaN FET을 사용해서 전원 스테이지를 설계할 때는 참고문헌 [8, 9]에서 제시하는 일반 레이아웃 권장사항을 따르는 것이 중요하다. 디자이너가 고려해야 할 순서는 언제나 공통 소스 인덕턴스(CSI), 전원 루프, 게이트 루프 인덕턴스 순이다[10]. 전원 스테이지는 기본적으로 블록으로 설계되며, 그런 다음에는 그림 3에서 보는 것과 같이 게이트 신호들을 컨트롤러 IC로 연결한다. 참고문헌 [11]에서는 전원 스테이지 블록으로 권장 레이아웃의 변수들에 대해서 설명하고 있다. 그러므로 컨트롤러 IC에 적합한 최적의 블록을 손쉽게 선택할 수 있다. 2위상 컨트롤러의 경우에는 두 가지 대안적인 디자인 중에서 선택해야 할 수 있다. 설계 기준은 통상적으로 하드 스위칭을 하는 제어 FET(스위치)을 동기 정류기보다 우선적으로 고려하는 것이다. 예를 들어서 벅 컨버터는 상측 FET의 게이트 루프로 기생 인덕턴스를 최소화하도록 레이아웃을 최적화해야 한다. 부스트 컨버터는 하측 FET으로 그렇게 해야 한다(그림 3).

[그림 3] 권장 레이아웃

맺음말

이 글에서는 GaN FET에 MOSFET 게이트 드라이버를 사용하는 것에 관해서 설명했다. 디자이너들은 호환이 가능한지 고려하고, 권장되는 변경 사항들을 따르고, GaN 기술의 잠재력을 최대한 이끌어낼 수 있도록 레이아웃을 최적화해야 한다. 이러한 가이드라인을 따름으로써 범용 게이트 드라이버 및 컨트롤러를 사용해서 GaN 기반 전원 컨버터를 성공적으로 대량생산할 수 있을 것이다.

[참고문헌]

[1] A. Lidow, M. De Rooij, J. Strydom, D. Reusch, and J. Glaser, GaN Transistors for Efficient Power Conversion, 3rd ed. John Wiley & Sons, 2019. ISBN: 978-1119594147.

[2] ST (June 2016). BAT54 datasheet. Small signal Schottky diodes.

[3] ON Semiconductor (Aug 2020). MM5ZxxxST1G Series, SZMM5ZxxxST1G Series datasheet. Zener Voltage Regulators.

[4] Texas Instruments (July 2017). UCC27212A-Q1 datasheet. UCC27212A-Q1 Automotive 120-V Boot, 4-A Peak, High-Frequency High-Side and Low-Side Driver.

[5] Renesas (Jan 2022). ISL81806 datasheet. 80V Dual Synchronous Buck Controller Optimized to Drive E-mode GaN FET.

[6] Analog Devices (May 2022). LTC7891 datasheet. 100 V, Low IQ, Synchronous Step-Down Controller for GaN FETs.

[7] Analog Devices (April 2023). LTC7890 datasheet. Low IQ, Dual, 2-Phase Synchronous Step-Down Controller for GaN FETs.

[8] Efficient Power Conversion (2021). How2AppNote 007. How to Design an eGaN FET-Based Power Stage with an Optimal Layout datasheet.

[10] Reusch, D. and Strydom, J. “Understanding the effect of PCB layout on circuit performance in a high frequency gallium nitride based point of load converter,” Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 16-21 March 2013, pp. 649?655.

[11] J.S. Glaser, A. Helou, “PCB Layout for Chip-Scale Package GaN FETs Optimizes Both Electrical and Thermal Performance,” IEEE Applied Power Electronics Conference and Exposition (APEC), 20-24 March 2022.

EPC, 저가형 전기자전거, 드론 및 로봇공학을 위한 GaN

조회수 98회 / EPC

EPC, 1mΩ 온-레지스턴스를 적용한 최초의 GaN FET

조회수 82회 / EPC

EPC, 나노초 내에 75A ~ 231A 레이저 다이오드를 제어하는 GaN FET로 첨...

조회수 164회 / EPC

EPC, 까다로운 공간 애플리케이션을 위한 40V 정격 방사선 강화 GaN FET

조회수 287회 / EPC

EPC, GaN 트랜지스터, 까다로운 우주 애플리케이션을 위해 최신 방사선 ...

조회수 573회 / EPC

EPC, 15단계 GaN 신뢰성 보고서를 통해 실제 애플리케이션에서 GaN 디바...

조회수 462회 / EPC

솔라네이티브, GaN 디바이스 기반의 새로운 마이크로 인버터로 태양광 ...

조회수 432회 / EPC

EPC, 높은 전력밀도 애플리케이션의 유연한 설계 지원하는 GaN 제품군

조회수 409회 / EPC

EPC GaN IC, 전기 모빌리티와 로보틱스 및 드론을 위한 모터 드라이브의...

조회수 482회 / EPC

PDF 다운로드

회원 정보 수정