고밀도 모듈식 전력 시스템을 위한 PCB 레이아웃 및 열 설계

글/조 아길라(Joe Aguilar), 바이코 수석 매니저겸 최고 엔지니어(Principal Engineer)

엄격한 전압 레귤레이션과 매우 높은 과도 슬루율이 요구되는 상황에서는 시스템 내의 모든 전압 강하 소스와 모든 전력 손실 소스가 아무리 작더라도 측정 가능한 부정적인 영향이 있을 수 있다. 따라서 PCB 레이아웃은 고성능 전력을 달성하는데 매우 중요하다.

이 글은 고성능 PCB 레이아웃에 대한 개괄적인 원칙을 제시하고 있다. 저자인 조 아길라(Joe Aguilar)는 열 설계 접근방식과 전력 분배 네트워크(PDN: Power Delivery Network)에 대한 개요를 소개하고, 감소된 임피던스로 높은 전류를 라우팅할 수 있는 전략과 효과적인 디커플링 커패시턴스를 설계하기 위한 중요 고려사항 등을 설명한다.

고성능 컴퓨팅을 위한 전력 설계: PCB 레이아웃의 중요성

전력 시스템 설계는 일반적으로 공급단에서 부하까지 전력을 공급하는데 필요한 컨버터와 개별 부품 및 액세서리 등에 초점을 두고, PCB(Printed Circuit Board)는 장착 및 라우팅 플레인으로 취급하면서 일반적인 PCB의 여러 작은 손실과 임피던스를 보상하기 위해 주로 피드백 및 제어 회로에 의존하는 경우가 많다. 그러나 최근 AI(Artificial Intelligence) 및 슈퍼컴퓨팅용 프로세서와 같은 고밀도 부하들이 보다 정교하고, 훨씬 빨라지면서 모든 구성요소들이 최대 성능을 발휘하도록 요구되고 있다.

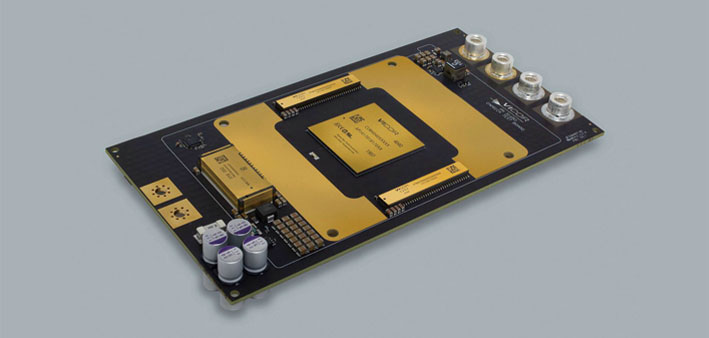

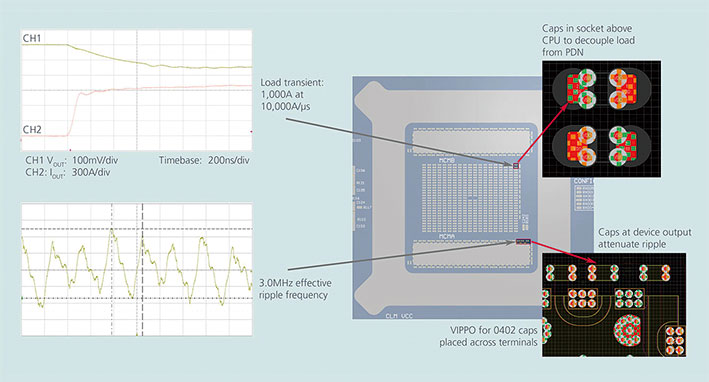

이러한 엄격한 전압 레귤레이션과 매우 높은 과도 슬루율이 요구되는 상황에서는 시스템 내의 모든 전압 강하 소스와 모든 전력 손실 소스가 아무리 작더라도 측정 가능한 부정적인 영향을 미칠 수 있다. 따라서 PCB 레이아웃은 고성능 전력을 달성하는데 매우 중요하다. 이 글에서는 고성능 PCB 레이아웃에 대한 개괄적인 원칙과 함께 열 설계 접근방식 및 전력 분배 네트워크(PDN: Power Delivery Network)에 대한 개요를 소개하고, 감소된 임피던스로 높은 전류를 라우팅할 수 있는 전략과 효과적인 디커플링 커패시턴스를 설계하기 위한 몇 가지 중요한 고려사항 등을 살펴보고자 한다. 그림 1은 이 글에서 사용한 테스트 및 데모를 위해 바이코(Vicor)에서 만든 설계이다.

[그림 1] 바이코의 이 테스트 보드는 고밀도 PCB에 장착된 하나의 PRM™ 레귤레이터 및 2개의 VTM™ 전류 멀티플라이어가 고성능 컴퓨팅 프로세서를 시뮬레이션하는 부하 모듈에 전원을 공급한다. 동작 시, 쿨링판 또는 히트싱크는 VTM 및 부하 모듈 위에 장착되고, 또 다른 히트싱크는 PRM에 장착된다.

열 설계

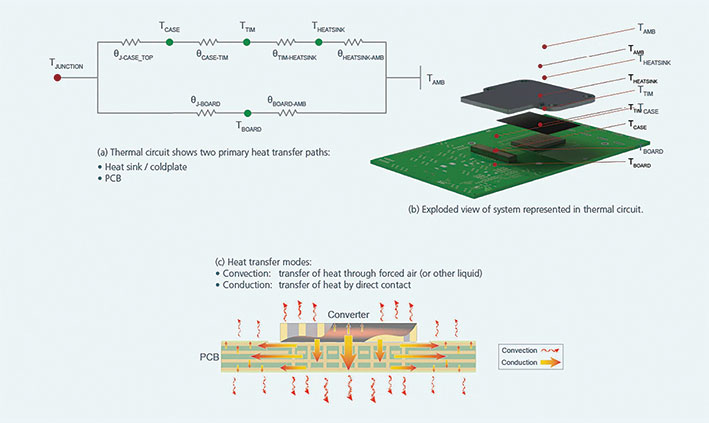

전력 시스템 설계에서 열 관리의 목표는 열을 발생시키는 접합부에서 주변 공기로 열을 효율적으로 이동시키는 것이다. 일부는 자연스럽게 그 흐름이 발생하지만, 일반적으로 기존 설계에서는 히트싱크와 팬을 추가해야 한다. 고밀도 시스템의 경우, PCB 자체를 열 전도체로 최대한 활용할 수 있도록 설계 프로세스 초기에 PCB에 중점을 둔 세밀한 열 전달 분석이 필요하다.

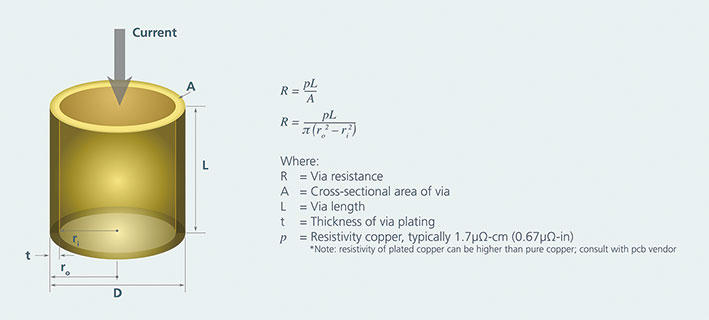

열 모델은 각 네트 또는 랜드의 각기 다른 열 임피던스로 인해 상당히 복잡해질 수 있다. 복잡성과 상관없이 열 모델은 구성요소의 내부 접합부에서 열을 이동시키기 위한 가장 낮은 임피던스 경로를 가진 네트를 식별하게 된다. 그런 다음, 설계자는 이 정보를 이용하여 해당 네트에 대한 구리를 증가시켜 열 전도를 극대화할 수 있다. 즉, 외부의 구리 플레인을 확장하고, 열 비아를 사용하여 표면적을 최소 이상으로 증가시켜 히트싱크의 전위를 높일 수 있다. 적절한 지점에 다양한 유형의 비아를 사용할 수도 있으며, 적층 및 매립형 비아나 VIPPO 및 전통적인 스루홀 비아 모두 설계자에게 효과적인 옵션이 될 수 있다.

전력 분배 네트워크 개요

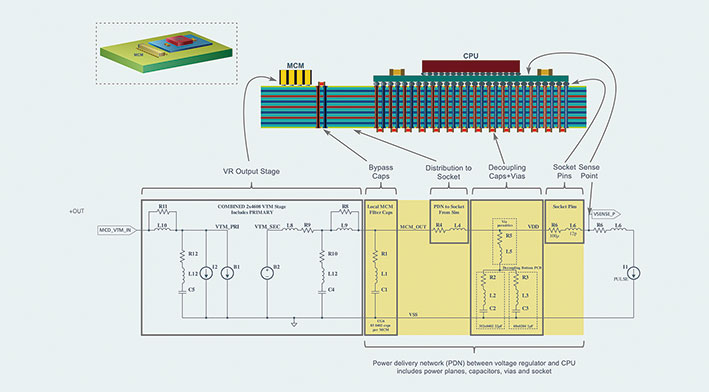

특히 PCB 내부의 전력 분배 네트워크 임피던스는 고밀도 컴퓨팅 전력 시스템에서 중점을 두고 있는 핵심 사항이다. 이러한 시스템은 매우 높은 주파수에서 작동한다. 일반적인 고성능 컴퓨팅 전력 시스템의 전력 분배 네트워크는 전압 레귤레이터의 출력과 감지 지점 사이에 여러 요소들로 구성되며, 이는 보통 다이 또는 BGA(Ball Grid Array) 인터커넥트 등 CPU 내부에 위치하고 있다. 바이패스 커패시터와 디커플링 커패시터, 그리고 연관된 비아 및 BGA 인터커넥트는 전력 분배 네트워크의 개별 구성요소를 구성한다. 강력한 슈퍼컴퓨팅 프로세서로 생성되는 고주파수 부하 단계는 너무 빠르기 때문에 제어 루프를 통해 전력 분배 네트워크에 미치는 영향을 최소화할 수 있는 방법은 거의 없다. 따라서 전력 분배 네트워크 설계가 무엇보다 중요하다.

[그림 3] 특히 높은 주파수와 큰 부하 단계에서 전압 레귤레이터와 CPU 부하 사이의 전력 분배 네트워크의 개별 구성요소 임피던스는 전력 설계의 효율성에 심각한 영향을 미칠 수 있다.

고전류 라우팅: 전력 분배 네트워크 임피던스 감소

전체 레이어 수와 전력 및 접지 전용 레이어 수 그리고 사용할 구리의 무게 등을 비롯해 PCB의 적층도 및 평면도를 미리 정의하는 것이 중요하다. 다음으로는, 신호 라우팅을 위한 연속 접지 플레인 전용 레이어를 식별해야 하며, 임피던스 제어 라우팅이 필요하거나 기생 제한 또는 기타 특별한 고려사항이 요구되는 모든 네트에 필요한 레이어를 정의해야 한다. 1,000A 이상을 소비하는 고전류 프로세서를 설계할 때는 이를 올바르게 수행하는 것이 중요하다.

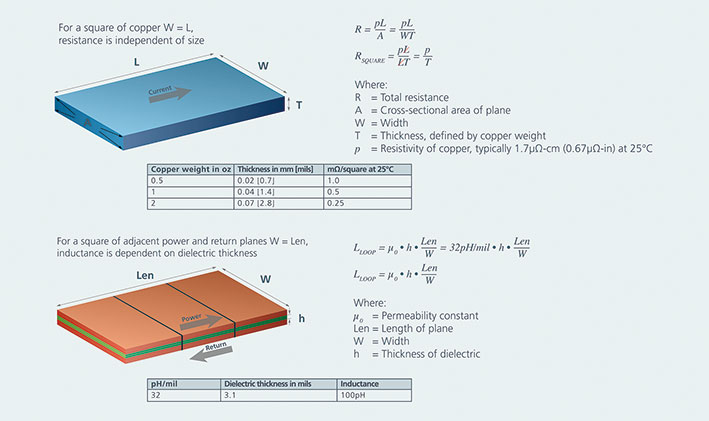

일부 평가 기법을 통해 이러한 초기 단계의 PCB 설계를 가속화할 수 있으며, 시뮬레이션을 사용하여 설계를 보다 쉽고, 정교화 할 수 있다. 구리 플레인의 저항률을 평가하는 자승법(Squares Method)은 간단하고 효과적인 기법 중 하나이다. 또한 자승법의 변형을 사용하여 인접한 전력 및 리턴 플레인의 인덕턴스를 추산할 수도 있다.

디커플링 커패시턴스

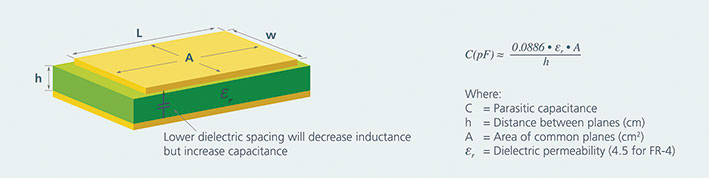

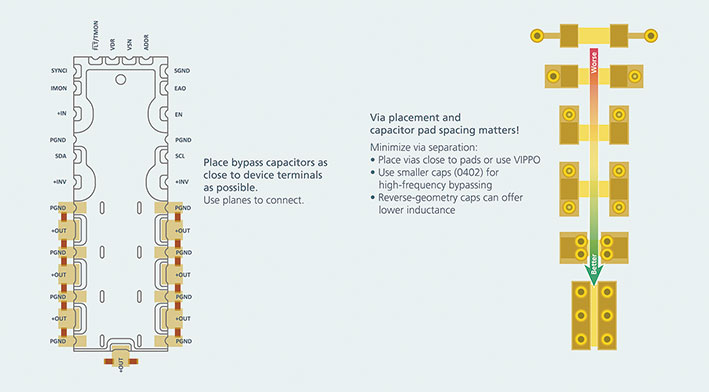

고밀도 전력 시스템은 고주파수 스위칭 노이즈를 필터링하기 위해 디커플링 커패시터를 신중하게 선택해야 한다. 이러한 종류의 애플리케이션은 매우 낮은 등가직렬 저항(ESR: Equivalent Series Resistance)과 적절하게 높은 자가공진 주파수(Self-Resonant Frequency)를 가진 커패시터가 필요하며, 이를 벗어나는 커패시터는 등가직렬 인덕턴스(ESL: Equivalent Series Inductance)로 인해 임피던스가 유도되어 고주파수 노이즈를 효과적으로 필터링하기 어렵다. 커패시턴스 값은 전반적으로 덜 중요할 수 있다.

10,000A/µs에서 1,000A 부하 단계를 처리하도록 설계된 시스템 사례에서, 전력 모듈에 매우 인접하게 배치된 0402 디커플링 커패시터는 리플을 감쇠하는 반면, 소켓에 있는 다른 커패시터는 전력 분배 네트워크에서 부하를 분리하는 것으로 나타났다.

전동화 트렌드를 주도하는 소형 전원 모듈

조회수 481회 / 바이코

MOSA, SOSA 및 VPX 개방형 아키텍처를 사용하는 표준 국방 플랫폼의 미래

조회수 4552회 / Matt Renola

전원 컨버터가 어떻게 로보틱스 혁신에 기여하는가?

조회수 1252회 / Maurizio Di Paolo Emilio

로봇 혁명을 촉진하는 바이코의 전력변환 혁신

조회수 1211회 / Vicor Corporation

고밀도 모듈식 전력 시스템을 위한 PCB 레이아웃 및 열 설계

조회수 1415회 / Joe Aguilar

항공우주 및 방위산업용 전력에 대한 FAQ

조회수 1379회 / Matt Renola

전력 소모가 급증하는 컴퓨팅 어플리케이션 솔루션

조회수 1293회 / Robert Gendron

로봇 혁명을 이끌 전력 변환 기술의 획기적 발전

조회수 1556회 / 바이코

모바일 로봇 성능 최적화

조회수 1409회 / Anna Giasson 외 1인

PDF 다운로드

회원 정보 수정