DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃 부품 배치 방법(2)

글/로옴코리아(https://www.rohm.co.kr/contactus)

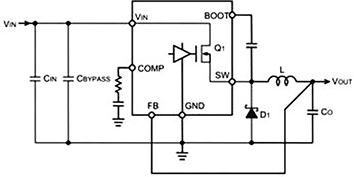

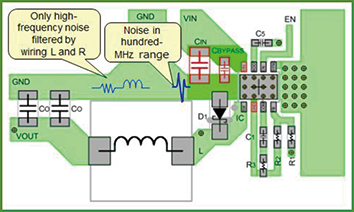

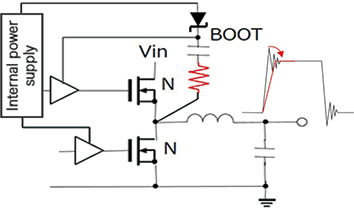

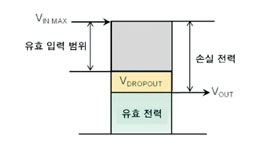

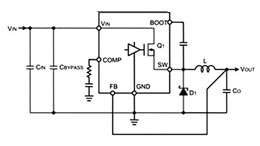

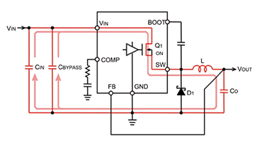

부품 배치에 대해 구체적으로 설명하겠다. 하기 기판 레이아웃은 「강압 DC/DC 컨버터 동작 시의 전류 경로」에서 설명했던 회로도이다(그림 11). 이 회로도를 염두에 두고 기판 레이아웃 예를 확인하자.

[그림 11] 기판 레이이웃 예시 회로

입력 콘덴서와 다이오드

레이아웃은가장 중요한 부품인 입력 콘덴서와 다이오드의 배치부터 시작한다. 기판 레이아웃에서 입력 콘덴서와 다이오드를 IC 단자와 동일한 면에, 가능한 IC에 가깝게 배치한다고 했다. 이는 매우 중요한 포인트이다.

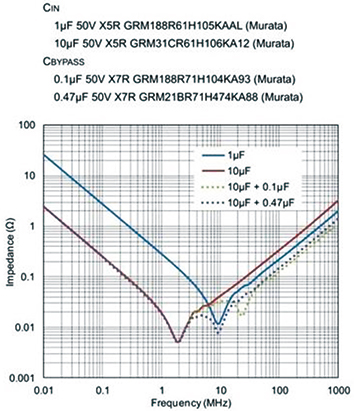

출력전류가 작은 전원(IO≤1A)일 경우, 입력 콘덴서는 용량치도 작아지므로, 세라믹 콘덴서 1 개로 CIN과 CBYPASS를 겸하는 경우가 있다. 이는 세라믹 콘덴서의 경우 용량치가 작아짐에 따라 주파수 특성이 우수해지기 때문이다. 단, 종류나 메이커에 따라 주파수 특성이 달라지므로, 실제로 사용하는 콘덴서의 주파수 특성을 확인해 두어야 한다.

CIN에 사용하는 대용량 콘덴서의 경우, 그림 12와 같이 일반적으로는 주파수 특성이 특별하게 우수한 제품은 아니므로, CIN에 병렬로 주파수 특성이 우수한 고주파 디커플링 콘덴서 CBYPASS를 배치할 필요가 있다. CIN과 CBYPASS를 조합함에 따라, 주파수 특성은 콘덴서 2개의 합성 특성이 된다.

[그림 12] CIN과 CBYPASS를 조합한 경우의 주파수 특성 비교

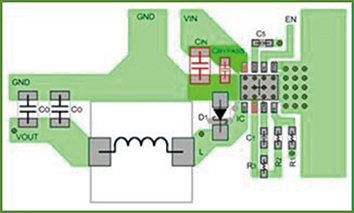

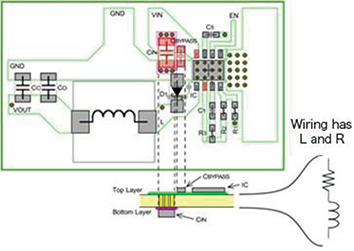

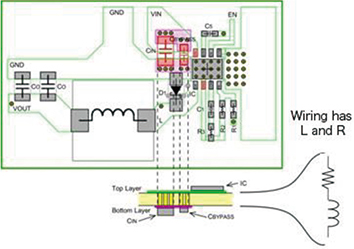

그럼, 실제 레이아웃을 참고로, 바람직한 예와 그렇지 못한 예를 들어 설명하겠다. 그림 13은 바람직한 입력 콘덴서의 레이아웃 예이다. CBYPASS를 IC 단자와 동일한 면에 가깝게 배치했다.

[그림 13] 바람직한 입력 콘덴서의 배치

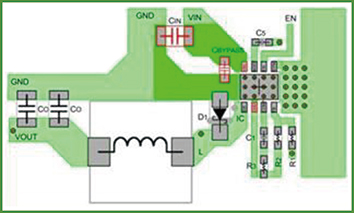

반면에, 그림 14는 타협점을 선택한 예이다. CBYPASS가 IC 단자와 동일한 면에 가깝게 배치되어 있어, 펄스 상태의 입력전류 대부분을 공급할 수 있다. 따라서, 대용량 콘덴서 CIN은 그림 14와 같이 2cm 정도 거리를 두어도 문제가 발생하지는 않겠지만, 앞서 설명한 바와 같이 가능한 IC에 가깝게 배치하는 것이 좋다.

[그림 14] CBYPASS가 IC와 동일한 면에서 가깝게 배치되어 있는 경우, CIN은 2cm 정도 거리를 두어도 무방

스페이스의 문제로 IC와 동일한 면에 CIN을 배치할 수 없는 경우에는, CBYPASS가 바르게 배치되어 있다는 조건 하에, 그림 15와 같이 비아(Via)를 통해 이면에 배치할 수 있다.

[그림 15] 비아를 통해 CIN을이면에 배치한 예(리플 전압의 증가가 우려된다.)

이러한 방법은, 노이즈 증가를 회피할 수는 있겠지만, 비아 저항의 영향으로 인해 대전류 시에 리플 전압이 증가할 가능성이 있으므로, 실제 확인이 필요하다. 그림 16은 CBYPASS와 CIN을 이면에 배치한 레이아웃이다.

[그림 16] CBYPASS 와 CIN을이면에 배치한 예. 비아 인덕턴스로 인해 노이즈 증가

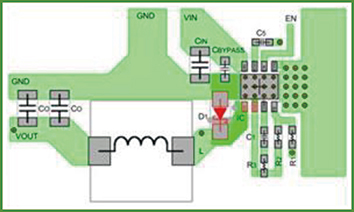

이 레이아웃은 비아의 인덕턴스 성분으로 인해 전압 노이즈가 증가하므로, 절대 이러한 레이아웃을 해서는 안 된다. 그림 17은 CBYPASS, CIN 및 다이오드 D1의 바람직한 레이아웃이다.

[그림 17] 바람직한 입력 콘덴서와 다이오드 배치 예

CBYPASS는 IC의 VIN 단자 및 GND 단자에 가깝게 배치하는 것이 중요하다. 단, 강압 컨버터의 경우는 CBYPASS를 IC에 가깝게 배치해도, CIN의 GND에는 수백 MHz의 고주파가 존재한다. 따라서 CIN의 GND와 출력 콘덴서 CO의 GND는 1cm ~ 2cm 정도 거리를 두고 배치할 것을 권장한다.

다이오드 D1도 IC 단자와 동일한 면에서 가깝게 배치한다. 다이오드는 폭넓은 배선을 사용하여 가장 짧게, IC의 스위칭 단자와 GND 단자에 직접 접속할 필요가 있다. 비아를 통해 이면에 배치하면, 비아의 인덕턴스로 인해 노이즈가 증가하므로, 절대 이 방법을 사용해서는 안 된다.

그림 18은 바람직하지 않은 다이오드의 레이아웃 예이다. CBYPASS와 IC의 VIN 단자 및 GND 단자와의 거리가 떨어져 있어, 배선 인덕턴스의 영향으로 전압 노이즈나 링잉이 발생한다.

[그림 18] 바람직하지 않은 다이오드의 배치 예

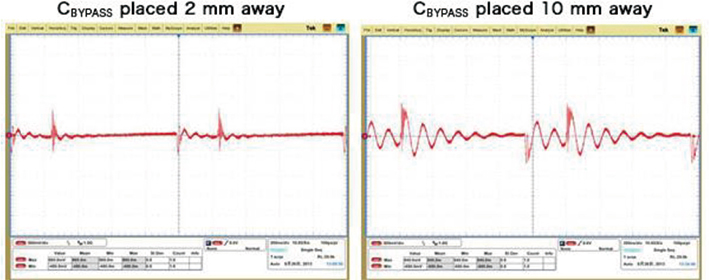

또한, 다이오드와 IC의 스위칭 단자 및 GND 단자와의 거리가 떨어져 있으므로, 배선 인덕턴스가 증가하여 스파이크 노이즈가 커진다. CBYPASS의 배치가 부적절한 경우, 즉,가깝게 배치되어 있지 않은 경우에는 배선 길이 및 비아로 인해 기생 인덕턴스가 증가하고, 스위칭에 따라 큰 링잉이 발생한다(그림 19).

또한, 입력 콘덴서까지의 루프가 안테나 역할을 하여, 주변으로 노이즈가 방사된다. 그림 19의 파형은 CBYPASS를 2mm 간격을 두고 배치한 경우와 10mm 간격을 두고 배치한 경우의 파형이다. 링잉이 커지는 것을 분명하게 알 수 있다.

[그림 19] CBYPASS의 거리와 링잉

레이아웃의 영향은 어떻게 배치했느냐에 따라 그대로 결과로 이어지게 된다. 실제로 레이아웃 작성 시에는 타협할 수밖에 없는 경우가 있을 것이다. 그러나, 타협점을 최저한으로 억제하여, 어디까지나 이상적인 레이아웃을 목표로 하여야 한다.

서멀 비아(Thermal via)

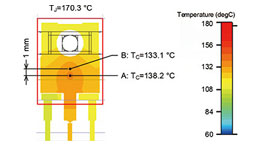

서멀 비아는 기판을 이용한 표면 실장 부품의 방열 효과를 향상시키는 방법으로 널리 알려져 있지만, 바르게 배치하지 않으면 충분한 효과를 얻을 수 없다.

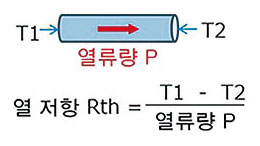

서멀 비아는 기판을 관통하는 구멍(Hole)을 만들고, 1층의 양면 기판일 경우 기판 표면과 이면의 동박을 연결함으로써 방열에 이용하는 면적과 체적을 늘려 열 저항을 낮추는 방법이다. 다층 기판의 경우, 여러 층간의 면을 연결하거나, 부분적으로 연결하는 층을 한정하는 방법이 있으며, 개념은 동일하다.

표면 실장 부품은 프린트 기판에 실장함으로써, 열 저항을 낮추는 것을 전제로 하고 있다. 열 저항은 방열기의 역할을 하는 프린트 기판 상의 동박 면적이나 두께, 또는 기판 두께나 재질에 의존한다. 기본적으로 넓고 두껍게, 전달되기 쉽게 함으로써, 방열 효과를 향상시킬 수 있다. 그러나 동박의 두께는 일반적으로 표준 사양에 준거하므로, 무턱대고 두껍게 할 수는 없다. 또한, 스페이스 절약이 기본 사항으로 요구되고 있어, 기판에서 방열용 면적을 원하는 만큼 취할 수도 없다. 실제로는 동박의 두께도 결코 두껍다고 할 수 없으므로, 일정 면적을 초과하게 되면 면적에 적합한 방열 효과를 얻을 수 없게 된다.

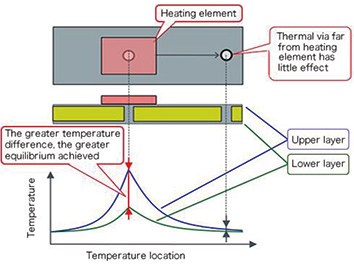

이러한 과제의 해결책 중 하나가 서멀 비아이다. 서멀 비아를 효과적으로 사용하기 위해서는 서멀 비아를 발열체에 가깝게, 예를 들어 부품의 바로 밑에 배치하는 것이 중요하다. 그림 20과 같이, 열의 평형성을 이용하는 것이므로 오도차가 큰 부분을 연결하는 것이 좋은 방법이다.

[그림 20] 서멀 비아의 열전도

* 서멀 비아의 배치

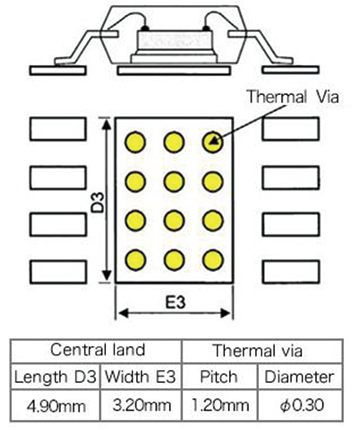

그림 21은 이면에 방열판이 노출되어 있는 타입의 IC 패키지 HTSOP-J8의 서멀 비아 레이아웃과 치수의 예이다. 서멀 비아는 열 전도율을 높이기 위해, 도금 충전 가능한 내경 0.3mm 정도의 작은 비아를 권장한다. Hole의 직경이 너무 크면 리플로 솔더링 공정에서 솔더 유입 문제가 발생할 가능성이 있으므로 주의가 필요하다.

[그림 21] 이면 방열 패키지의 서멀 비아 치수 및 배치 예

서멀 비아는 1.2mm 정도의 간격으로 패키지의 이면 방열판 바로 밑에 배치한다. 만약, 이면 방열판의 바로 밑만으로 방열이 부족한 경우에는, IC 주변에도 서멀 비아를 배치한다. 이러한 경우, 되도록 IC에 가깝게 배치하는 것이 중요하다.

인덕터

인덕터의 레이아웃은 EMI를 최소한으로 억제해야 한다. 또한, 자기(磁氣) 부품으로서의 인덕터 특성을 잘 이해해야 한다.

인덕터에 전류가 흐르면 자력선(磁力線)이 발생한다. 이 자력선이 도체, 프린트 기판의 경우에는 동박을 통과하면, 그 부분에 과전류가 발생한다. 즉, 인덕터 근처에 도체가 있으면, 과전류로 인해 문제가 발생하는 경우가 있다. 과전류가 자력선을 상쇄하는 또한, 인덕터는 발열하는 부품이므로 주의해야 한다. 인덕터에 전류가 흐르면, 권선의 저항 성분과 기타 손실로 인해 발열한다. 인덕터가 고온이 되면 부재의 열화이외에도, 페라이트 코어의 경우에는 퀴리 온도(Curie temperature)를 넘으면 인덕턴스가 급격하게 감소한다. 기준으로서 전류 정격 및 저항치의 SPEC이 제시되어 있으므로, 실장 시에는 방열을 고려할 필요가 있다.

동박이 신호선인 경우는, 과전류로 인해 신호에 노이즈가 전달되는 경우가 있어, 회로 동작에 악영향을 미칠 가능성이 있다.

* 인덕터의 배치

인덕터는 스위칭 노드로부터의 복사 노이즈를 최소한으로 억제하기 위해, 입력 콘덴서만큼은 아니더라도 가능한 IC에 가깝게 배치해야 한다. 배선 저항의 저감과 방열을 위해 동박 면적을 너무 넓게 설정하면, 동박이 안테나의 역할을 하는 경우가 있어 EMI가 증가하므로, 동박 면적을 필요이상으로 넓게 해서는 안 된다.

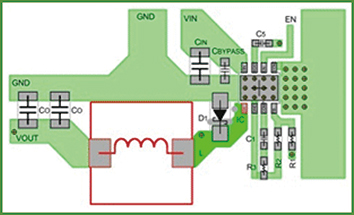

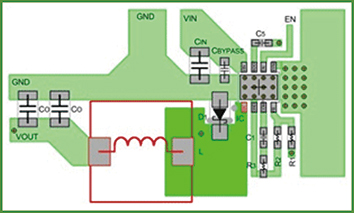

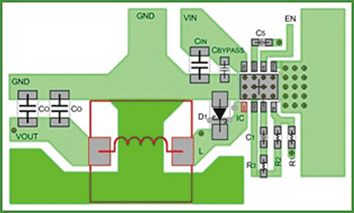

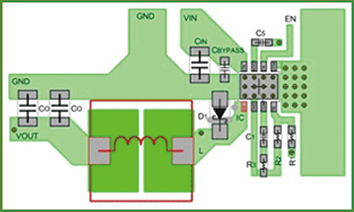

그림 22는 EMI의 관점에서 배선 면적을 고려한 레이아웃, 그림 23은 필요 이상으로 배선을 넓게 배치하여 좋지 않은 레이아웃이다.

[그림 22] 바람직한 인덕터의 배선 예

[그림 23] 필요이상으로 넓은 동박 면적 (좋지 않은 인덕터의 배선 예)

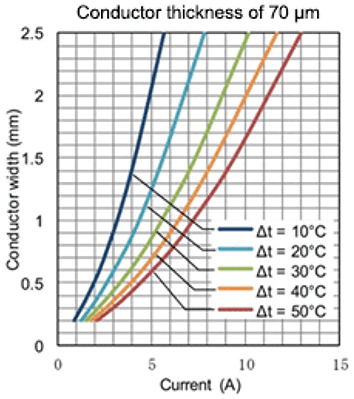

구체적인 배선 폭을 결정하기 위해서는 전류 내량을 하나의 기준으로 삼을 수 있다. 그림 24, 그림 25는 일정 전류가 흐를 때의 도체 폭과 자기 발열로 인한 온도 상승을 나타낸 그래프이다.

[그림 24] 도체 두께 35μm일 때, 도체 폭과 전류에 의한 온도 상승

[그림 25] 도체 두께 70μm일 때, 도체 폭과 전류에 의한 온도 상승

예를 들어, 2A의 전류를 도체 두께 35μm의 배선에 흘릴 경우, 20℃의 온도 상승으로 억제하기 위해서는 0.53mm의 도체 폭으로 대응할 수 있다. 단, 배선은 주변 부품의 발열이나 주위 온도의 영향을 받으므로, 충분한 마진을 둘 필요가 있다. 예를 들어, 1 온스(35μm) 기판에서는 1A 당 1mm 폭 이상, 2 온스(70μm) 기판에서는 1A 당 0.7mm 폭 이상을 권장한다.

인덕터의 바로 밑에 GND나 다른 배선을 배치해서는 안 된다(그림 26). 앞서 설명한 바와 같이, 자력선이 도체인 GND 층을 통과하여 과전류가 발생하므로, 자력선의 상쇄 효과로 인해 인덕터 값의 저하 및 Q의 저하(손실 증가)가 발생하기 때문이다.

[그림 26] 좋지 않은 인덕터 아래 배선 예

GND 이외의 신호선에서도 과전류로 인해 신호에 스위칭 노이즈가 전달될 가능성이 있으므로, 인덕터 바로 밑에는 배선을 해서는 안된다. 어쩔 수 없이 신호선을 배선해야 하는 경우에는 자력선의 누설이 작은 폐자로(閉磁路) 구조의 인덕터를 사용한다. 단, 문제가 발생하지 않는지에 대해서는 실측을 통해 반드시 확인하자.

또한, 인덕터 단자의 배선 간 스페이스에도 주의해야 한다. 그림 27과 같이 단자의 배선 간 거리가 가까우면, 스위칭 노드의 고주파 신호가 부유 용량을 통해 출력으로 용량성이 유도된다.

[그림 27] 좋지 않은 인덕터 단자간 배선 예

출력 콘덴서

출력 콘덴서는 입력 콘덴서와 마찬가지로, 강압 DC/DC 컨버터에 필수인 콘덴서이다. 출력의 평활화, 안정화, 그리고 리플 전압에 영향을 미친다.

* 출력과 입력 콘덴서 전류의 차이점

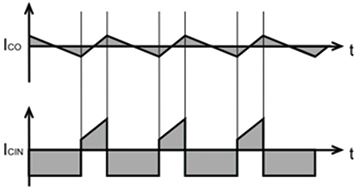

출력 콘덴서는 입력 콘덴서와 마찬가지로, 강압 DC/DC 컨버터에 필수인 콘덴서이다. 출력의 평활화, 안정화, 그리고 리플 전압에 영향을 미친다. 먼저, 입력 콘덴서 CIN과 출력 콘덴서 CO에 흐르는 전류의 차이점을 확인하겠다. 그림 28의 ICO가 출력 콘덴서, ICIN이 입력 콘덴서의 전류 파형이다.

입력 콘덴서에는 비교적 큰 전류가 급격하게 반복하여 흐르지만, 출력 콘덴서는 출력전압을 중심으로 출력 리플 전압과 연동하여 완만한 충방전을 반복한다. 이는 출력 라인에 직렬로 인덕터가 삽입되어 있기 때문이며, 인덕터 L과 CO는 출력 필터의 역할도 한다.

[그림 28] 출력 콘덴서(lCO), 입력 콘덴서 (ICIN)의 전류 파형

* 출력 콘덴서의 배치

CO의 GND 접속은 CIN의 GND 접속 부분에서 1 ~ 2cm 떨어진 위치에, 가능한 인덕터에 가깝게 배치한다(그림 29).

[그림 29] 출력 콘덴서 CO의 배치 예

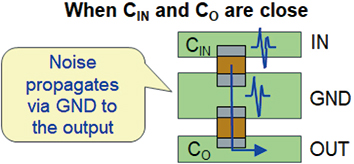

앞서 설명한 바와 같이, 입력 콘덴서에는 급격한 상승/하강 전류가 반복하여 흐르므로, CIN이 접속되는 GND 패턴에는 수백 MHz의 고주파가 유입된다. 당연히 CO가 접속되는 GND 패턴은 동일한 GND 패턴이므로, CIN의 접속 부분에 가깝게 CO를 배치하면, 입력의 고주파 노이즈가 CO를 통해 출력으로 전달될 가능성이 있다. 그림 30은 이러한 내용을 모식화한 것이다.

[그림 30] CIN과 CO가 가까운 경우, GND을 통해 노이즈가 전달

CO의 GND를 CIN의 GND 로부터 1 ~ 2cm 정도 거리를 두는 이유는, 박막 배선의 인덕턴스와 저항 성분이 필터의 역할을 하여, 고주파 노이즈를 저감시킬 수 있기 때문이다. 즉, 기생 성분을 잘 이용하는 것이다.

피드백 경로(귀환 경로)

피드백 경로(귀환 경로)란, 출력 안정화를 위해 출력전압을 전원 IC의 FB 단자에 패드백하기 위한 경로이다. 피드백 경로의 배선은 신호 배선 중에서도 특히 주의가 필요하다.

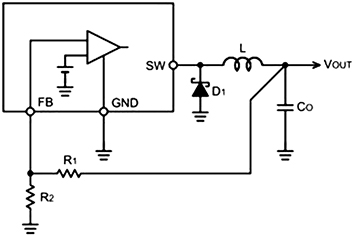

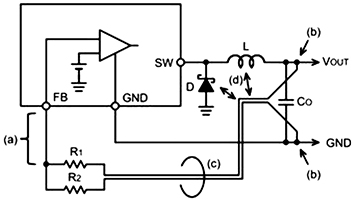

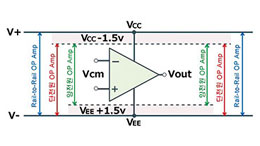

그림 31의 회로도가 나타내는 바와 같이, 출력전압은 배선을 통해 저항에 의해 분압되어 전원 IC의 FB PIN = 에러 앰프의 입력에 피드백된다. 전원 IC는 그 전압 정보를 바탕으로 출력전압의 안정화를 실행한다. 이러한 피드백 경로가 중요한 이유는, 만약 실제의 출력전압이외의 노이즈나 변동이 에러 앰프에 전달되면, 정확한 출력 안정화가 불가능할 뿐만 아니라, 조건에 따라서는 발진 등 동작이 불안정해지는 경우가 있기 때문이다. 따라서 피드백 경로는 깨끗한 신호를 피드백시킬 수 있도록 고려해야 한다. 피드백 경로의 배선 시에는 주의사항이 있다(그림 32).

[그림 31] 피드백 경로(VOUT→R1 / R2→FB)

[그림 32] 피드백 경로 배선 시의 주의점

• 피드백 신호 배선에 노이즈가 유입되면 출력 전압에 오차가 발생하여, 경우에 따라서는 동작이 불안정 해진다.

• 피드백 신호를 입력하는 IC의 FB PIN은 임피던스가 높으므로, 이 PIN과 저항 분압 회로의 분압 노드는 가능한 짧은 배선으로 연결한다. : 그림 32의 (a)

• 출력전압을 검출하는 부분은, 출력 콘덴서의 양쪽 끝이나 출력 콘덴서보다 앞에서 검출한다.: 그림 32의 (b)

• 출력에서 저항 분압기까지의 배선은 평행하고 짧게 하는 것이 노이즈의 유입을 억제할 수 있다.: 그림 32의 (c)

• 인덕터 및 다이오드의 스위칭 노드로부터 거리를 두고 배선한다.: 그림 32의 (d)

• 인덕터 및 다이오드의 바로 밑, 파워 스위치계의 배선과 평행하게 배선하지 않는다(다층 기판에서도 동일).

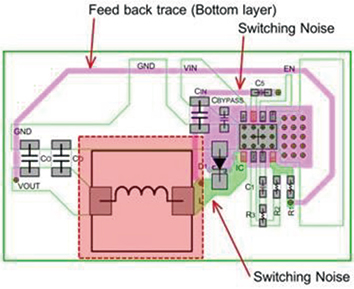

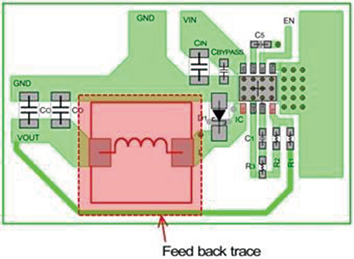

그림 33은 이러한 점에 주의하여 레이아웃한 배선 예로, 비아를 통해 피드백 경로의 배선을 이면으로 이동하여 스위칭 노드로부터 거리를 둔 레이아웃의 예이다.

[그림 33] 피드백 경로의 레이아웃 예

레이아웃을 보면 알 수 있듯이, 상기의 조건을 완벽하게 만족하는 배선은 그렇게 간단하지 않다. 주의사항에서는 언급하지 않았지만, 배선의 기본은 가능한 짧게한다. 따라서, 피드백 배선을 무턱대고 길게 하여 회로 면적으로부터 거리를 두는 것은 좋은 방법이라고 할 수 없다. 이러한 경우에는, 피드백 신호의 배선을 이면에 전개하는 것도 대처 방법 중 하나이다(그림 33).

그림 34는 좋지 않은 예이다. 피드백 경로가 인덕터에 평행하게 레이아웃되어 있으므로, 인덕터 주변에 발생하는 전계로 인해 피드백 경로에 노이즈가 유도된다.

실제로 다른 부품과의 관계 때문에 어쩔 수 없이 이상적인 배치 및 배선이 불가능한 경우가 있다. 이러한 경우에는 이상적인 배치의 기본이 무엇인지를 생각하여, 최대 공약수적인 타협점을 찾아내야 한다.

[그림 34] 좋지 않은 피드백 경로의 레이아웃 예

그라운드

그라운드(이하, GND) 배선은 대부분의 부품에 각각 필요한 배선이므로, 레이아웃 시에는 고려할 점이 많다. 또한, 강압 DC/DC 컨버터 회로의 경우, 제어 회로에 연결되는 출력전압의 피드백 등의 신호계와 대전류를 스위칭하는 파워계의 분리가 중요하며, 이는 GND 배선에서도 마찬가지이다.

* 아날로그 소신호 GND와 파워 GND

그라운드(이하, GND) 배선은 대부분의 부품에 각각 필요한 배선이므로, 레이아웃 시에는 고려할 점이 많다. 또한, 강압 DC/DC 컨버터 회로의 경우, 제어 회로에 연결되는 출력 전압의 피드백 등의 신호계와 대전류를 스위칭하는 파워계의 분리가 중요하며, 이는 GND 배선에서도 마찬가지이다.

GND는 회로(기판)의 어떤 위치에 있더라도, 전위로서는 동일하지만, 아날로그 신호와 디지털 신호가 혼재하는 회로에서는 아날로그 GND와 디지털 GND를 분리하여, 디지털 신호로 인한 노이즈가 미세한 아날로그 신호에 전달되지 않도록 하는 방법이 사용된다. 스위칭 전원 회로에 있어서도 개념은 동일하다. 예를 들어 라인의 전압치가 직접적으로 출력 정밀도로 이어지는 피드백 경로는 스위칭 노드에 발생하는 노이즈의 영향을 최소한으로 억제하는 등의 배려가 필요하다.

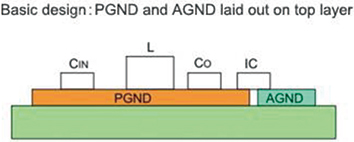

호칭은 여러가지가 있지만, 본 자료에서는 피드백 경로와 같은 노이즈에 민감한 라인에 관련된 GND를 아날로그 소신호 GND(AGND), 스위칭 노드 등 큰 전류가 스위칭하는 라인에 관련된 GND를 파워 GND(PGND)라고 하겠다.

가장 중요한 것은, AGND 와 PGND는 분리되어 있어야 한다는 점이다. 동일한 전위이고, 최종적으로는 접속되지만, 스위칭에 의해 큰 전류가 리턴하는 GND와 제어 신호의 GND를 분리하여 간섭을 배제하는 것이다.

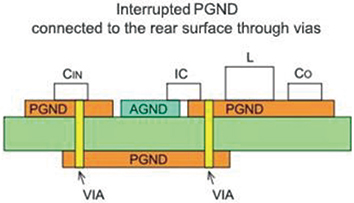

PGND는 기본적으로 Top Layer에 1 줄로 레이아웃 한다(그림 35). 그러나 부품 배치 등의 관계로 인해 어쩔 수 없이 1줄로 배치할 수 없는 경우가 있다. 그러한 경우에는 PGND를 분리하고 비아를 통해 이면이나 내층을 이용하여 접속하는 것도 가능한다(그림 36). 단, 비아의 저항 및 인덕턴스의 영향으로, 손실 증가 및 노이즈 악화의 가능성이 있으므로, 실제 기기에서 충분히 검증해야 한다.

[그림 35] 기본적인 GND 레이아웃의 예

[그림 36] 비아를 통해 PGND를 연결한 예

* GND Plane

GND Plane은 어느 정도의 면적을 가진 GND 배선을 뜻한다. 이면이나 내층에 GND Plane을 배치하는 것은 기본적으로 DC 손실의 경감, 실드, 방열이 목적이며, GND 로서는 어디까지나 보조적인 역할을 하는 것이다.

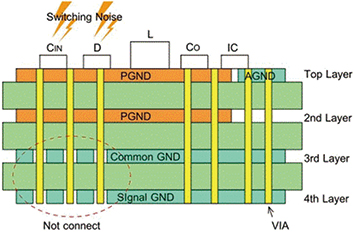

다층 기판에서 내층이나 이면에 GND Plane을 배치하는 경우에는, 고주파 스위칭 노이즈가 많은 입력 및 다이오드 PGND 와의 접속에 주의해야 한다. 그림 37과 같이, 3rd Layer에 Common GND, 4th Layer에 Signal(신호) GND가 있는 경우, 이들과 PGND의 접속은 고주파 스위칭 노이즈가 적은 출력 콘덴서 CO 부근의 PGND 로 접속한다. 노이즈가 많은 입력 콘덴서 CIN이나 다이오드 D 부근의 PGND 로 접속해서는 안 된다.

[그림 37] 다층 기판에서의 PGND와 신호 GND의 접속 예와 주의점

2nd Layer에 DC 손실 경감을 위한 PGND Plane이 있는 경우, Top Layer의 PGND와 2nd Layer를 다수의 비아로 접속하여, PGND의 임피던스를 작게 할 필요가 있다.

대부분의 DC/DC 컨버터 IC는 AGND(SGND)와 PGND의 2가지 GND 단자를 구비하고 있다. 이는 동일한 이유에서 IC 내부에서도 신호계와 스위치(파워)계가 분리되어 있기 때문이다. 또한, 동일한 전위일 필요가 있으므로, 최종적으로는 접속한다. IC의 AGND와 PGND는 1 포인트에서 접속하는 것이 중요하다.

기판 레이아웃에 있어서의 노이즈 대책

지금까지 설명한 바와 같이, 스위칭 전원 회로에 있어서는 노이즈를 억제하여 안정적인 동작을 확보함과 동시에, 다른 디바이스에 EMI가 미치는 영향을 최소한으로 억제하는 기판 레이아웃이 필요하다. 기본적인 부품 배치 및 배선 레이아웃 외에도, 기판 레이아웃에 관련된 노이즈 대책이 몇가지 있다.

코너 배선

배선 패턴에는 코너 배선이 꼭 필요하며, 이러한 코너의 배선 방법에 따라 EMI의 악화를 초래하는 경우가 있다. 그림 38은 코너 배선의 좋고 나쁨을 표시한 것이다. 코너 배선을 직각으로 하면, 코너에서 임피던스가 변하게 된다. 이로 인해 전류가 불안정해져 반사라고 하는 파형의 흔들림이 발생하게 된다. 스위칭 노드 등 주파수가 높은 배선에서는 이러한 반사로 인해 EMI가 악화될 가능성이 있다.

[그림 38] 코너 배선 레이아웃의 좋고 나쁨

코너 배선은 직각으로 구부려서는 안되고, 45°나 원호 (円弧)를 그리듯 둥굴리는 것이 바람직하다. 구부리는 반경이 클수록 임피던스의 변화는 작아진다.

노이즈 단자 전압(전도성 에미션)

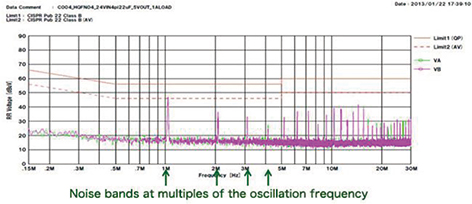

노이즈 단자 전압은 입력 라인에 피드백되는 노이즈로, 전도성 에미션이라고도 한다. 주로 발진 주파수의 배수로 노이즈 대역이 나타난다. 이러한 노이즈는 페라비트 비즈나 π형 필터를 삽입함으로써 억제할 수 있다. 이러한 노이즈 대책 부품은 억제하고자 하는 대역(저감하고자 하는 노이즈)에 일치하는 부품으로 선정해야 한다. 이를 위해서는 노이즈를 확인하고 주파수의 기준을 정해둘 필요가 있다. 그림 39는 노이즈 단자 전압의 측정 데이터 예이다.

[그림 39] 노이즈 단자 전압의 측정 데이터 예

노이즈 전계 강도(방사 노이즈)

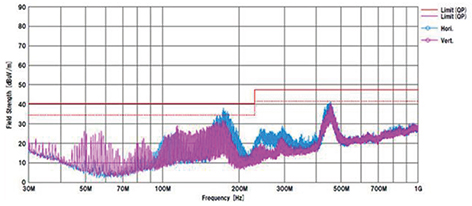

또 한가지 검토해야 하는 노이즈로, 노이즈 전계 강도(방사 노이즈 )가 있다. DC/DC 컨버터의 방사 노이즈는 스위치 ON/OFF 파형의 기울기와 링잉으로 인해 발생하고, 그 대역은 100MHz ~ 300MHz이다.

스위칭 상승/하강 시의 링잉은 주로 MOSFET와 입력 콘덴서 사이의 배선 인덕턴스가 원인이 되며, 인덕턴스의 크기가 노이즈에 영향을 미친다. 입력 콘덴서의 배치 편에서 설명한 바와 같이, 입력 콘덴서의 배치와 배선을 최적화함으로써, 노이즈의 레벨을 낮출 수 있다.

DC/DC 컨버터 회로의 방사 노이즈가, 탑재 기기로서 만족해야 하는 규격을 초과했을 때의 대책으로서, 스위칭 파형을 완만하게 하는 방법과 스너버 회로를 추가하는 방법이 있다.

그림 40은 방사 노이즈의 측정 예이다. 노이즈 레벨의 한계가 적색 선으로 표시되어 있으며, 이 예에서는 200MHz 정도의 영역에서 다소 좋지 않은 결과를 나타내고 있다.

[그림 40] 방사 노이즈의 측정 데이터 예

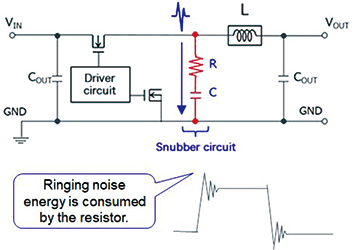

스너버 회로의 추가

스너버 회로의 추가는 노이즈를 저감하기 위해 자주 사용되는 방법이다. 스위칭 노드의 노이즈 저감인 경우에는, 출력에 스너버 회로를 추가하지만, 입력의 노이즈에 대해서는 입력에 추가한다. 본 예에서는 스위칭 노드에 RC를 추가하여, 스위칭으로 인한 링잉의 고주파 에너지를 저항에서 소비시켜 링잉을 흡수한다(그림 41).

[그림 41] 스너버 회로와 동작의 예

단, 스너버 회로의 추가로 인해 손실이 발생하므로 주의해야 한다. 효과를 높이기 위해 콘덴서의 용량을 늘리면, 저항은 그 전력을 허용해야 한다. 하기는 스너버 손실의 계산 식과 예이다.

스너버 회로 손실 계산의 예 :

스너버 저항 10Ω, 스너버 콘덴서 1000pF, 입력전압 12V, 발진 주파수 1MHz 일 경우 저항의 허용 손실

![]()

1000pF × 122 × 1MHz = 0.144W

* 저항의 정격전력은 MCR18(3216) : 0.25W 이상 필요

하이 사이드 스위치에 Nch MOSFET를 사용하는 IC에는 대부분의 경우 BOOT 단자가 있다. 이는 출력전압을 Bootstrap 회로에 공급하고, 하이 사이드 MOSFET에 충분한 게이트 드라이브 전압을 인가하는 기능이다.

BOOT 단자는 스위칭 노드에 연결되어 있으므로, 여기에 저항을 삽입함으로써 하이 사이드 MOSFET ON 시의 턴-온을 완만하게 할 수 있어, 스위치 ON 시의 노이즈를 완화시킬 수 있다. 단점으로는 스위칭 시간이 느려지므로, MOSFET의 스위칭 손실이 증가한다(그림 42).

[그림 42] Bootstrap 회로에 저항을 삽입하는 예

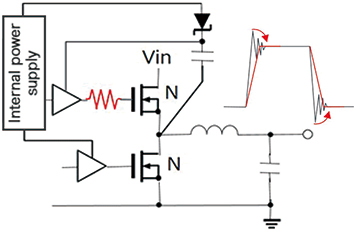

하이 사이드 MOSFET의 노이즈 대책

하이 사이드 MOSFET의 게이트 드라이버와 게이트 사이에 저항을 삽입함으로써, 게이트 차지를 제한하여 하이 사이드 MOSFET의 상승/하강을 완만하게 함으로써 ON/OFF 시의 노이즈를 저감하는 방법이다(그림 43).

[그림 43] 외장 하이 사이드 MOSFET에 게이트 저항을 삽입한 예

단점으로는 Bootstrap의 저항 추가와 마찬가지로, MOSFET의 스위칭 손실이 증가한다. 또한, 이 방법은 스위치 내장 타입의 IC에는 사용할 수 없다. 스위치 외장 타입의 컨트롤러 IC를 사용하는 구성에서만 이용 가능한 방법이다.

맺음말

본 고에서는 강압 DC/DC 컨버터의 실장 기판 레이아웃에 관한 포인트에 대해 설명했다. 가장 기본이 되는 것은 ‘레이아웃 시에는 항상 배선은 가능한 짧게’를 염두에 두고 있어야 한다.

설계한 회로가 적절하고, 부품에도 문제가 없는데도 불구하고, 기판 실장 시 예상보다 성능이 좋지 않거나, 최악의 경우 동작하지 않는다는 문제에 직면하는 경우에는 먼저, 기판 레이아웃이 적절한지를 확인하라. 이러한 경우는 의외로 적지 않다.

무엇보다도 회로 설계부터 기판 설계, 프로토 타입, 양산과 수정 및 재설계를 최대한 줄이는 것은 더할 나위 없이 중요하다. 이를 위해서는 기판 설계를 포함한 설계 품질을 향상시키는 것이다.

실제의 기판 레이아웃 시에는 부품의 배치 및 배선에 제약이 발생하는 경우가 많다. 그렇지만 억제해야 할 포인트를 레이아웃 설계에 확실히 반영하는 것은 매우 중요하다. 이상적인 상태에서 벗어난 경우에는 반드시 실측하여 문제의 유무를 확인해야 한다. 또한, 기판 레이아웃 설계는 다층 기판, 전자파 등이 있으므로, 어떤 의미에서는 3차원적 이미지로의 확장이 요구되는 설계라고 할 수 있다. 그리고 이미지를 확장하기 위해서는 실제로 설계하고 실측하는 작업을 반복하는 것이 중요하다.

※ 내용 중에 궁금하신 점은 로옴코리아(https://www.rohm.co.kr/contactus)로 직접 문의하시기 바랍니다.

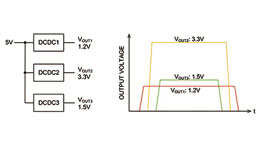

범용 전원 IC로 전원 시퀀스를 실현하는 회로

조회수 879회 / 로옴코리아

열 설계와 기술 트렌드의 변화

조회수 1304회 / 로옴코리아

평활 후의 DC/DC 안정화 방식

조회수 1083회 / 로옴코리아

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃 부품 배치 방법(2)

조회수 2464회 / ROHM

DC/DC 컨버터 기판 레이아웃의 기초_기판 레이아웃의 대원칙(1)

조회수 1658회 / ROHM

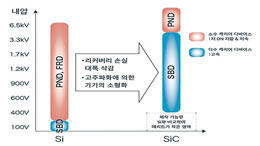

SiC 파워 디바이스란?

조회수 5321회 / ROHM

열 저항 RthJC의 측정 방법과 사용법

조회수 3339회 / 로옴코리아

연산증폭기와 비교기란?

조회수 4454회 / ROHM

열 저항과 방열의 기본

조회수 11338회 / ROHM

PDF 다운로드

회원 정보 수정