고속 증폭기 테스트 시 핵심 고려 사항

글/데이빗 브랜든(David Brandon), 롭 리더(Rob Reeder), ADI

대부분의 실험실에서는 신호 발생기나 스펙트럼 분석기 같은 싱글 엔디드(single ended) 장비를 사용해서 고속 차동 증폭기 드라이버나 컨버터의 왜곡을 측정한다. 따라서 증폭기 드라이버 상의 2차 고조파 왜곡(HD2)이나 짝수차 혼변조 왜곡(IMD2) 같은 짝수 차수 왜곡을 측정하려면 싱글 엔디드 테스트 장비를 증폭기 드라이버의 차동 입력 및 출력에 연결하기 위한 발룬이나 감쇠기 같은 추가적인 장치들이 필요하다.

이 글에서는 불일치하는 신호에 대한 수학적 계산을 통해 위상 불평형(phase imbalance)이 중요한 이유에 대해 살피고, 위상 불평형이 짝수 차수 성분을 얼마나 증가시키는지, 다시 말해 얼마나 악화시키는지에 대해 알아본다. 이와 함께 서로 다른 고성능 발룬과 감쇠기를 사용했을 때 증폭기 성능 지표(HD2, IMD2)에 얼마나 영향을 미치는지 설명한다.

수학적 배경

아날로그-디지털 컨버터(ADC), 증폭기, 믹서, 발룬처럼 차동 입력을 사용하는 고속 디바이스를 테스트할 때, 크기와 위상 불평형은 꼭 확인해야 할 중요한 사양이다.

500MHz 이상의 주파수를 사용하는 아날로그 신호 체인 디자인을 설계할 때는, 수동이든 능동이든 모든 디바이스가 어느 정도 고유한 불평형을 내재하고 있다는 점에 주의를 기울여야 한다. 여기서 500MHz라는 숫자 자체가 중요한 것은 아니고, 경험적으로 대다수의 디바이스들이 이 지점부터 위상 평형이 이탈하기 시작한다는 뜻이다. 그러니 디바이스에 따라서 이 주파수는 이보다 훨씬 낮을 수도, 높을 수도 있다.

아래의 간단한 수학 모델을 사용해서 좀더 자세히 살펴보자.

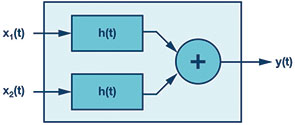

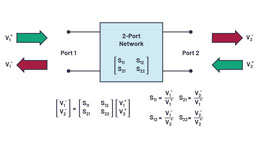

[그림 1] 2개의 신호 입력을 사용할 때의 수학 모델

ADC, 증폭기, 발룬, 혹은 다른 어떤 디바이스로 입력 x(t)가 신호를 싱글 엔디드에서 차동으로 또는 그 반대로 변환한다고 가정해 보자. 신호 쌍인 x1(t)와 x2(t)는 사인파이므로, 차동 입력 신호는 다음 공식과 같이 표현할 수 있다:

![]()

만약 그렇지 않다면, 이들 소자에서의 불평형 때문에 동작 주파수 범위에 걸쳐서 ADC의 짝수 차수 왜곡 테스트 결과가 크게 차이가 날 것이다.

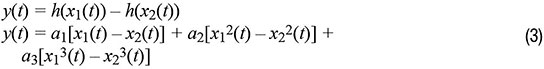

ADC 혹은 다른 어떤 능동 부품이든 대칭형 3차 전달 함수로 간단히 모델링할 수 있다:

![]()

그러면 다음과 같이 표현할 수 있다:

불평형이 전혀 없는 이상적인 경우라고 한다면, 위의 간단한 시스템의 전달 함수를 다음과 같이 표현할 수 있을 것이다:

x1(t)와 x2(t)가 완벽하게 평형을 이룬다면 이들 신호는 크기가 같고(k1= k2= k) 정확하게 180°의 위상차(φ = 0°)를 가질 것이다.

![]()

전력에 삼각함수 등식을 적용하고 주파수 같은 항들을 취합하면 다음의 결과를 얻을 수 있다:

![]()

이는 차동 회로에서 친숙한 결과이다: 짝수 고조파는 이상적인 신호를 취소하는 반면, 홀수 고조파는 그렇지 않다.

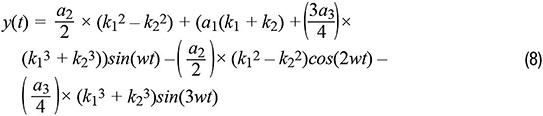

이번에는 두 입력 신호가 크기 불평형은 있고 위상 불평형은 없다고 가정해 보자. 이 경우라면 k1 ≠ k2이고, φ = 0이다.

![]()

공식 (3)에 공식 (7)을 대입하고 다시 삼각함수 등식을 대입하면 다음과 같다:

공식 (8)을 통해 2차 고조파가 크기 항인 k1과 k2의 제곱의 차에 비례한다는 것을 알 수 있다. 간단히 정리하면 다음과 같다:

![]()

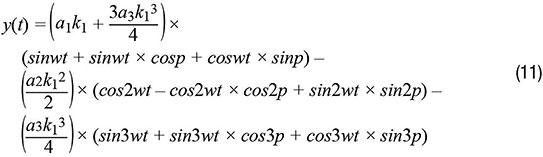

이번에는 공식 (7)과는 반대로, 두 입력 신호가 위상 불평형만 있고 크기 불평형은 없다고 가정해 보자. 그러면 k1 = k2이고 φ ≠ 0이다.

![]()

공식 (3)에 공식 (10)을 대입하면 다음과 같다:

공식 (11)에서는 2차 고조파 진폭이 크기 항 k의 제곱에 비례한다는 것을 알 수 있다.

![]()

뒤로 돌아가서 공식 (9)와 공식 (12)를 비교하고 삼각함수 등식이 좋은 형태라고 가정한다면, 이는 다음과 같이 요약할 수 있다: ‘2차 고조파는 크기 불평형보다는 위상 불평형에 의해서 더 심하게 영향을 받는다.’

이유는 이렇다. 위상 불평형은 공식 (12)에서 보듯이 2차 고조파가 k1의 제곱에 비례하고, 크기 불평형은 공식 (9)에서 보듯이 2차 고조파가 k1 및 k2의 제곱의 차에 비례한다. k1과 k2는 거의 같기 때문에 대체로 이 차이는 작으며, 특히 제곱한 숫자와 비교하면 더욱 그렇다.

고속 증폭기 테스트

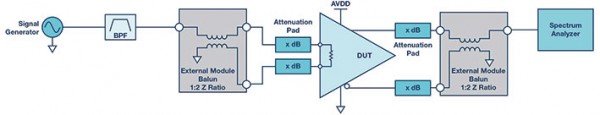

그러면 이제 어려운 수학 공식은 뒤로 하고, 그림 2에서와 같은 활용 사례를 살펴보자. 이것은 실험실에서 차동 증폭기에 대해서 HD2 왜곡을 테스트할 때의 테스트 설정을 나타낸다.

[그림 2] 고속 증폭기 HD2 테스트 설정

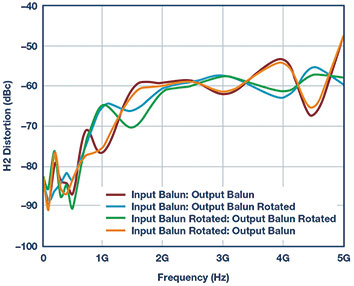

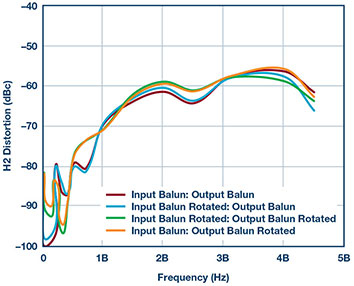

언뜻 간단해 보여도 자세히 들여다 보면 그리 간단치 않다. 그림 3은 이 테스트 설정으로 차동 증폭기, 발룬, 감쇠기 같은 것들을 동일한 것들을 사용해서 얻은 HD2 테스트 결과를 보여준다. 이 테스트는 발룬 방향을 다양하게 하는 방법으로 간단한 위상 불일치가 어떻게 HD2 주파수 스윕에 걸쳐서 각기 다른 결과를 나타내는지 보여주기 위한 것이다. 이 셋업에는 2개의 발룬이 사용되므로, 연결 방향을 바꾼다면 4가지 시나리오가 가능하다. 그림 3은 그 테스트 결과를 나타낸 것이다.

[그림 3] 벤더 1A의 발룬 제품을 사용해서 다양한 발룬 방향으로 수행한 HD2 성능 테스트

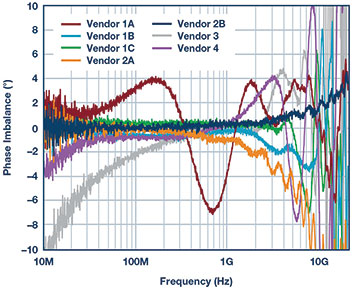

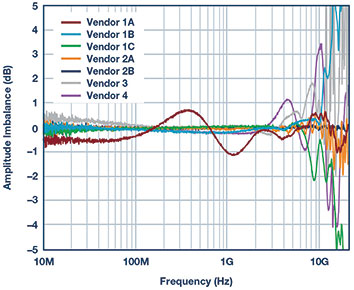

그림 3에서는 HD2 왜곡 곡선이 차이가 난다는 것을 알 수 있다. 이는 특히 위상 및 크기 불평형과 관련해서 발룬의 성능을 좀더 살펴볼 필요가 있다는 것을 뜻한다. 아래의 두 그림은 여러 제조회사들의 다양한 발룬 제품들의 위상 및 크기 불평형을 보여준다. 이 불평형 테스트 측정을 위해 네트워크 분석기를 사용했다.

그림 4와 그림 5에서 빨간색 선은 그림 3에서 HD2 왜곡 데이터를 얻는 데 사용된 발룬이다. 이 발룬은 벤더 1A 발룬으로서, 대역폭이 가장 높고 통과대역 평탄성이 우수하나, 동일한 10GHz 주파수 테스트 대역에서는 다른 발룬들에 비해 위상 불평형이 나쁘다.

[그림 4] 다양한 발룬 제품의 위상 불평형

[그림 5] 다양한 발룬 제품의 크기 불평형

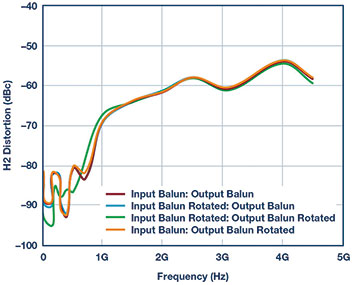

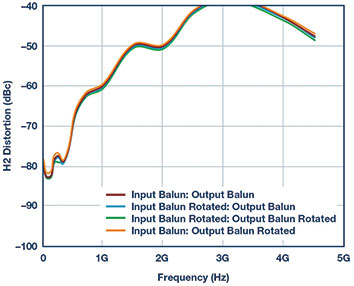

그림 4와 그림 5는 위에서 위상 불평형이 가장 낮은 발룬인 벤더 1B와 벤더 2B 제품을 사용해서 HD2 왜곡을 다시 테스트한 것이다. 그림 7에서는 불평형 특성이 좋아짐에 따라 HD2 왜곡 편차도 그만큼 줄어든다는 것을 알 수 있다.

[그림 6] 벤더 1B 발룬을 사용해서 다양한 발룬 방향으로 수행한 HD2 성능 재시험

[그림 7] 벤더 2B 발룬을 사용해서 다양한 발룬 방향으로 수행한 HD2 성능 재시험

[그림 8] 벤더 2B 발룬을 사용해서 다양한 발룬 방향으로 수행한 HD3 성능 테스트

위상 불평형이 짝수 차수 왜곡에 얼마나 직접적으로 영향을 미치는지 더 살펴보기 위해서, 그림 8은 위의 HD2와 동일한 조건으로 HD3 왜곡을 측정한 것을 보여준다. 4개의 선이 예상대로 거의 동일하다는 것을 알 수 있다. 따라서 위의 수학 공식에서 살펴본 바와 같이, HD3 왜곡은 신호 체인의 불평형에 그렇게 민감하지 않다는 것을 알 수 있다.

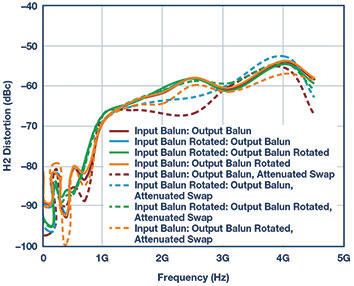

지금까지는 그림 2에서와 같이 입력 및 출력에 연결된 감쇠기 패드가 고정돼 있고, 발룬 방향을 측정하는 동안 바꾸지 않았던 것으로 가정하였다. 다음 그림은 감쇠기를 입력과 출력을 바꿨을 때 벤더 2B의 발룬 성능만 테스트한 것인데, 그림 7에서 나타난 것과 동일한 곡선을 보여준다. 이들 4개 트레이스는 그림 9에서 점선으로 표시되었는데, 이 테스트에서는 차이가 더 심하다는 것을 알 수 있다. 또한 차동 신호 쌍의 양쪽 중 어느 한쪽에서의 작은 불일치라도 높은 주파수에서는 문제가 된다는 것을 알 수 있다. 이러한 테스트를 할 때는 테스트 조건을 상세히 기록하는 것이 좋다.

[그림 9] 벤더 2B 발룬을 사용해서 다양한 발룬 방향에 대해, 그리고 감쇠 패드를 뒤바꿔서 수행한 HD2 성능 테스트

맺음말

기가헤르츠(GHz) 대역에서 완전 차동 신호 체인을 개발할 때는 감쇠기 패드, 발룬, 케이블, PCB 트레이스를 비롯한 모든 것이 중요하다. 이 글에서는 이를 수학적으로 살펴보고 또 고속 차동 증폭기를 테스트한 결과를 살펴보았다. 어떤 부품이나, 또는 그 부품을 만든 제조회사를 탓하기 전에, PCB 레이아웃이나 랩 테스트에 신중을 기하는 것이 필요하다.

궁극적으로, 얼마만큼의 위상 불평형을 허용할 수 있는지 스스로 확인해 볼 필요가 있다. 예를 들어, 발룬 제품을 선택한다고 할 때, x GHz에서 위상 불평형이 x°라고 한다면 이는 부품이나 시스템에서 어느 정도의 성능 저하에 해당하는 것일까? 선형성 성능에 있어서 dB가 어느 정도의 손실 또는 저하를 입게 될 것인가?

이러한 것들은 대답하기 어려운 질문들이다. 신호 체인 상의 모든 것이 완벽하게 매칭을 이루고 있다면 어떠한 짝수 차수 왜곡도 일으키지 않을 것이다. 또한 위상 불평형이 x°라고 했을 때 선형성에 있어서 손실(HD2 저하)이 x dB라고 하는 어떤 경험적 원칙이나 공식을 알 수 있다면 좋을 것이다. 하지만 그렇게 될 수가 없다. 왜 그럴까? 능동 소자이든 수동 소자이든 모든 소자는 특성적으로 차동이고 일정한 형태의 근원적인 위상 불일치를 내포하기 때문이다. IC 설계를 내부적으로 완벽하게 평형을 이루게 하거나 또는 케이블을 완벽하게 매칭되는 길이로 절단할 수 있는 방법은 없다. 그러므로 이러한 불일치가 아무리 작더라도 시스템에 사용되는 주파수가 높아질수록 그러한 불일치는 점점 더 차이가 나게 될 것이다.

이러한 IC를 설계하는 제조회사들은 이러한 IC 레이아웃 불일치를 작게 하기 위해서 부단히 노력하고 있다. 마찬가지로 사용자들 역시 이러한 제품을 선택할 때 실험실에서 신중한 테스트를 거쳐야 할 것이다.

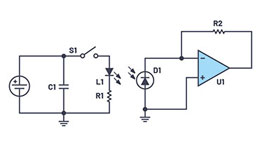

레귤레이트 된 48V를 12V로 첫 번째 단의 효율을 대폭 향상시키는 결합 ...

조회수 443회 / Alexandr Ikriannikov 외 1인

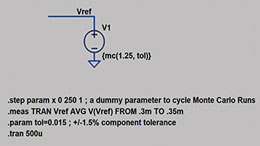

LTspice를 사용하여 복잡한 회로에 대한 통계학적 허용오차 분석 모델링...

조회수 1830회 / Steve Knudtsen

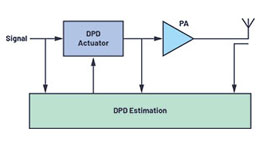

실제 유용한 디지털 전치왜곡 솔루션 설계 방법

조회수 1157회 / Steve Summerfield 외 1인

보다 우수한 성능의 산소포화도 측정기 설계 방법

조회수 8132회 / Robert Finnerty

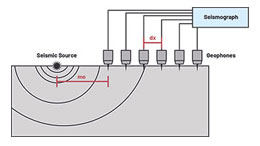

지진 탐사 및 에너지 탐사 애플리케이션용 저잡음 저전력 DAQ 솔루션

조회수 1210회 / David Guo

RF 신호 체인의 주요 특성 및 성능 지표

조회수 4675회 / Anton Patyuchenko

PCB 공간 제약 문제 해결하는 모놀리식 벅-부스트 컨버터 및 LED 드라이버

조회수 1661회 / Kyle Lawrence

퍼시비어런스 화성 탐사선과 극한환경을 위한 고신뢰성 기술

조회수 1348회 / Analog Devices

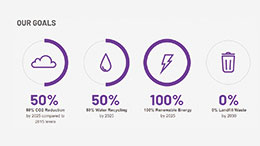

아나로그디바이스(ADI), 반도체 업계 ESG 경영 선도한다

조회수 1254회 / ADI

PDF 다운로드

회원 정보 수정