지진 탐사 및 에너지 탐사 애플리케이션용 저잡음 저전력 DAQ 솔루션

글/데이비드 구오(David Guo) 제품 AE, 스티븐 시에(Steven Xie) 제품 AE, 아나로그디바이스(Analog Devices, Inc.)

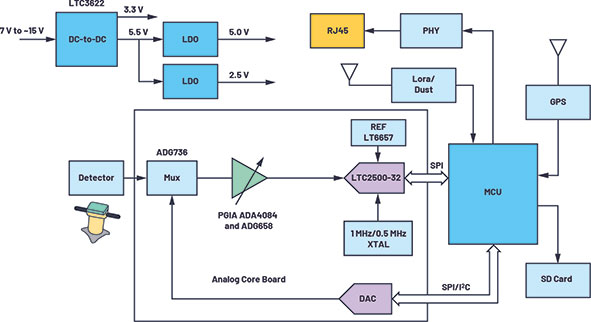

정밀 데이터 수집(DAQ) 시스템은 다양한 산업용 애플리케이션에 널리 사용된다. 일부 DAQ 애플리케이션은 저전력 소모와 극히 낮은 잡음을 중요하게 요구할 수 있다. 지진 탐사 애플리케이션이 그러한 예이다. 이를 통해 추출한 지진 데이터는 구조물 건전성 모니터링, 지구물리 연구, 석유 탐사, 산업 현장 및 주택의 안전성 같은 다양한 애플리케이션에 활용될 수 있다.[1]

DAQ 신호 체인의 요구사항

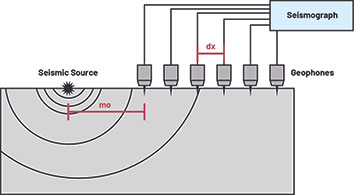

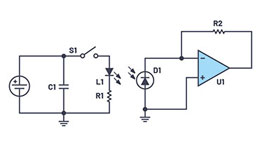

수진기(seismic geophone)는 땅의 진동 신호를 전기 신호로 변환하는 전기기계적 변환 장치이다. 수진기는 고분해능 지진 탐사에 사용하기에 적합하다. 지상에 일련의 수진기 어레이를 설치해서 지진파가 층리면(bedding plane) 같은 불연속적 표면에 반사되어서 되돌아오는 시간을 측정한다(그림 1).

[그림 1] 지진원과 수진기 어레이

수진기로부터 작은 값의 출력 신호를 포착하기 위해서는 감도가 높은 DAQ 신호 체인을 설계해야 한다. 300Hz ~ 400Hz의 제한된 평탄형 저역통과 대역폭 범위 내에 총 rms 잡음이 1.0µV rms여야 하고, THD는 약 -120dB 정도여야 한다. 또한 이 지진계는 배터리로 구동되므로 전력 소모를 약 30mW로 맞춰야 한다.

이 글에서는 다음과 같은 요구조건을 충족하는 두 가지 신호 체인 솔루션을 제안한다:

• PGIA의 이득: 1, 2, 4, 8, 16

• 프로그래머블 광대역 필터를 통합한 ADC 사용

• RTI 잡음: 이득 = 1일 때 1.0µV rms(300Hz ~ 400Hz, -3dB 대역폭)

• THD: 이득 = 1일 때 -120dB

• CMRR: 이득 = 1일 때 100dB 이상

• 전력 소모(PGIA + ADC): 33mW

• 자체 테스트용 2차 채널

DAQ 신호 체인 솔루션

하나의 정밀 ADC만을 사용해서 이 모든 특성과 이렇게 낮은 잡음 및 THD를 달성할 수 없으며, 마찬가지로 PGIA만을 사용해서 이렇게 낮은 잡음과 저전력을 달성할 수 없다. 하지만 ADI의 정밀 증폭기와 정밀 ADC를 결합하면 이러한 요구 조건을 충족하는 신호 체인을 설계할 수 있다.

잡음과 왜곡이 적고 전력 소모가 낮은 PGIA를 설계하기 위해서는 초저잡음 증폭기 ADA4084-2나 제로 드리프트 증폭기 ADA4522-2가 권장할 만하다.

초고정밀 ADC의 경우, 24비트 시그마-델타 ADC AD7768-1이나 32비트 SAR ADC LTC2500-32가 적합하다. 이들 ADC는 다양한 DAQ 애플리케이션의 요건들을 충족하도록 평탄형 저역통과 FIR 필터를 통합하여 구성가능한 ODR을 제공한다.

지진 신호 체인 솔루션: ADA4084-2 PGIA와 AD7768-1 사용

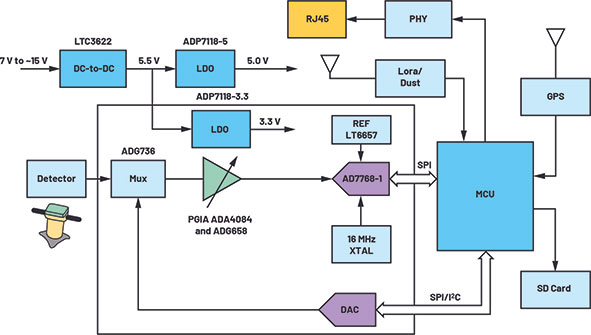

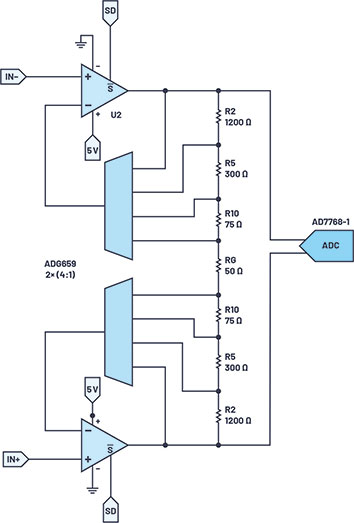

그림 2는 ADA4084-2 PGIA와 AD7768-1을 사용한 신호 체인 솔루션을 보여준다. ADA4084-2, ADG658, 0.1% 저항들을 사용해서 최대 8개의 서로 다른 이득 옵션이 가능하면서 잡음과 THD가 낮은 PGIA를 설계할 수 있다. AD7768-1은 단일 채널, 저전력, -120dB THD 제품이다. 리플이 낮은 프로그래머블 FIR과 DC ~ 110.8kHz 디지털 필터가 특징이며, 레퍼런스 디바이스로서 LT6657을 사용한다.

[그림 2] ADA4084-2 PGIA와 AD7768-1, 그리고 MCU 필터링을 사용한 신호 체인 솔루션

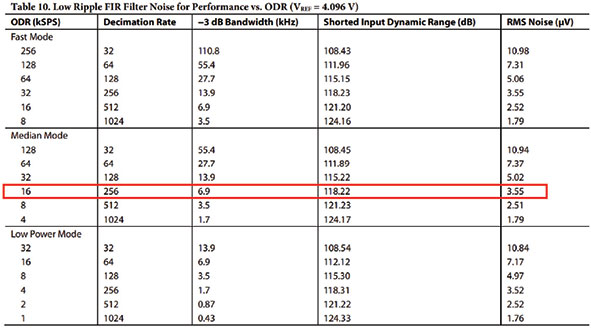

AD7768-1은 저전력 모드일 때 10mW의 전력 소모로 1kSPS의 ODR로 동작하면서 1.76µV의 rms 잡음을 나타낸다. 최종적으로 1.0µV rms 잡음을 달성하기 위해서는 중간 정도의 전력소모 모드에서 이를 테면 16kSPS 같은 더 높은 ODR로 동작하면 된다. AD7768-1을 더 높은 변조 주파수로 실행하면 잡음 플로어는 낮추는 대신 전력 소모가 높아진다(그림 3). MCU 소프트웨어에 평탄형 저역통과 FIR 필터 알고리즘을 구현해서 높은 대역폭 잡음을 제거하고 최종적 ODR을 1kSPS로 데시메이션할 수 있다. 그러면 최종적인 rms 잡음은 3.55µV의 약 1/4, 다시 말해 0.9µV가 될 것이다.

[그림 3] MCU 포스트 필터링을 사용해서 AD7768-1의 ODR을 목표 잡음에 맞게 밸런싱할 수 있다.

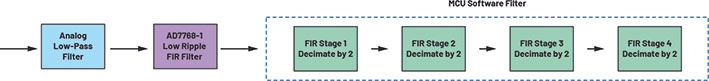

일례로, 그림 4와 같이 MCU 소프트웨어 FIR 필터를 작성해서 성능과 그룹 지연을 절충할 수 있다.

[그림 4] MCU 포스트 FIR 필터 스테이지

[그림 5] ADA4084-2 PGIA와 LTC2500-32를 사용하는 신호 체인 솔루션

[그림 6] LTC2500-32 평탄형 저역통과 필터의 다운샘플링 팩터별 잡음 수치

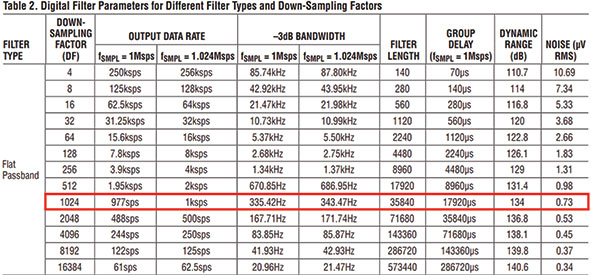

지진 신호 체인 솔루션: ADA4084-2 PGIA와 LTC2500-32 사용

LTC2500-32는 구성가능 디지털 필터를 통합한 저잡음 저전력 고성능 32비트 SAR ADC이다. 32비트 디지털 필터링을 통해 잡음과 INL이 낮은 출력을 제공하므로, 지진 탐사나 석유 탐사에 사용하기에 적합하다.

신호 포착 시 안정화 시간을 최소화하고 스위치 커패시터 입력 SAR ADC 선형성을 극대화하기 위해서는 고 임피던스 소스를 버퍼링 해야 한다. 최상의 성능을 달성하기 위해서는 LTC2500-32의 아날로그 입력을 구동할 수 있게 버퍼 증폭기를 사용해야 한다. 디스크리트 PGIA 회로는 LTC2500-32를 구동하여 낮은 잡음과 낮은 THD 둘 다를 달성할 수 있도록 설계되어야 하는데, 이는 PGIA 단락에서 소개한다.

PGIA 구현

PGIA 회로의 주요 사양은 다음과 같다:

• 전원: 최소 5V

• AD7768-1은 전력 소모가 19.7mW이므로, 33mW의 전력 소모 목표를 충족하려면 PGIA 회로의 전력 소모가 13.3mW 미만이어야 한다.

• 잡음: 이득 = 1일 때 잡음은 AD7768-1의 1.78µV rms의 약 1/10인 0.178µV rms이어야 한다.

PGIA 토폴로지는 3가지가 있다:

• 통합형 PGIA 사용

• 계측 증폭기를 통합하고 있는 디스크리트 PGIA 사용

• 연산 증폭기를 통합하고 있는 디스크리트 PGIA 사용

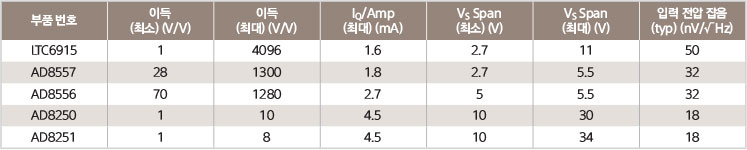

표 1은 ADI의 디지털 PGIA 제품 목록을 나타낸 것이다. LTC6915가 IQ0가 가장 낮고, 잡음 밀도는 50nV/√Hz이며, 430Hz 대역폭 내에서 적분 잡음은 1.036µV rms로서 목표로 하는 0.178µV rms를 넘는다. 그러므로 통합형 PGIA는 좋은 선택이 아니다.

[표 1] 디지털 PGIA

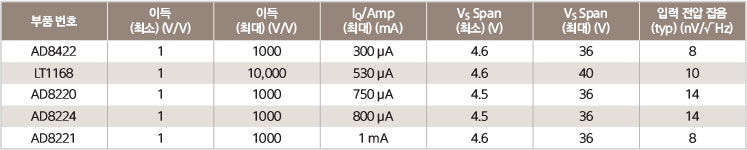

표 2는 300µA IQ AD8422를 비롯한 계측 증폭기 제품들의 목록이다. AD8422는 430Hz 대역폭 내에서 적분 잡음이 1.645µV rms이다. 따라서 이 역시 좋은 선택이 아니다.

[표 2] 계측 증폭기

잡음 시뮬레이션

LTspice®를 사용해서 디스크리트 PGIA의 잡음 성능을 시뮬레이트할 수 있다. 적분 잡음 대역폭은 430Hz이다. 표 4는 서로 다른 두 가지 PGIA에 AD7768-1을 사용할 때의 잡음 시뮬레이션 결과를 보여준다. ADA4084 솔루션이 잡음 성능이 더 우수하다는 것을 알 수 있다. 특히 높은 이득일 때 그렇다.

디스크리트 PGIA에 연산 증폭기 사용

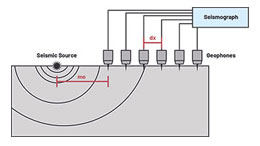

‘프로그래머블 이득 계측 증폭기: 적합한 솔루션 찾기’라는 제목의 기술 기사는 다양한 통합형 PGIA에 대해서 설명하고, 디스크리트 PGIA를 특정 요건을 충족하도록 설계하기 위한 가이드라인을 제안한다.[2] 그림 7은 디스크리트 PGIA 회로의 블록 다이어그램이다. ADG659/ADG658을 선택하면 낮은 값의 커패시턴스와 5V 전원을 사용할 수 있다.

[그림 7] 디스크리트 PGIA의 블록 다이어그램

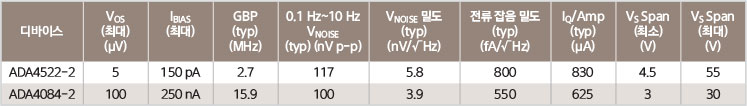

연산 증폭기의 사양에서는 IQ(채널당 1mA 미만)와 잡음(6nV/√Hz 미만의 전압 잡음 밀도)이 중요하다. ADA4522-2와 ADA4084-2는 정밀 연산 증폭기로서 괜찮은 선택이다. 표 3은 이들 제품의 특징을 보여준다.

[표 3] 저잡음 저전력 연산 증폭기

이득 저항의 경우, 1.2kΩ/300Ω/75Ω/25Ω 저항을 선택하면 1/4/16/64의 이득을 얻는다. 저항을 높이면 잡음이 증가하고, 저항을 낮추면 전력 소모가 늘어난다. 다른 이득 구성이 필요할 때는 이득 정확도를 달성하도록 저항을 신중하게 선택해야 한다.

차동 입력 ADC는 감산기의 역할을 한다. 이 ADC의 CMRR은 100dB 이상이므로 시스템 요구사항을 충족한다.

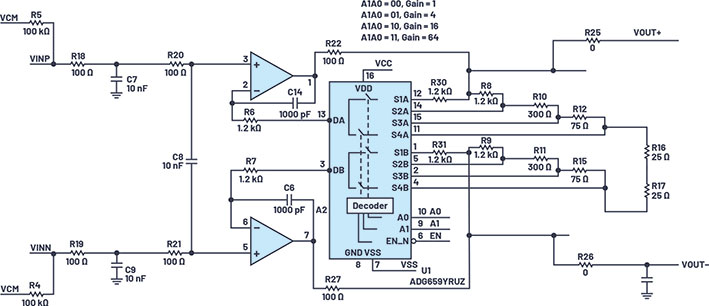

LTC2500-32를 구동하기 위한 루프내 보정 회로

AD7768-1은 구동에 필요한 프리차지 증폭기(pre-charge amplifier)를 통합하고 있다. LTC2500-32 같은 SAR ADC에는 드라이버로서 고속 증폭기를 사용하도록 권장된다. 또한 이 DAQ 애플리케이션은 대역폭 요구가 낮으므로, LTC2500-32를 구동하기 위해서 정밀 증폭기(ADA4084-2)를 사용하는 루프내 보정(in-loop compensation) 회로가 권장된다. 그림 8은 LTC2500-32를 구동하기 위한 루프내 보정 PGIA를 보여준다. 이 PGIA는 다음과 같은 특징을 갖는다:

[그림 8] LTC2500-32를 구동하기 위한 PGIA

• R22/C14/R30/C5와 R27/C6/R31/C3은 루프내 보정 회로에 보다 우수한 안정성을 달성하는 데 있어서 중요한 소자들이다.

• ADG659에서, A1/A0 = 00에 이득 = 1이면, 상단 증폭기의 피드백 경로는 증폭기 출력 → R22 → R30 → S1A → DA → R6 → AMP -IN이다.

• ADG659에서, A1/A0 = 11에 이득 = 64이면, 상단 증폭기의 피드백 경로는 증폭기 출력 → R22 → R8 → R10 → R12 → S4A → DA → R6 → AMP -IN이다.

이 PGIA를 LTC2500-32EVB에 연결해서 성능을 확인할 수 있다. 서로 다른 수동 소자 값(R22/C14/R30/C5와 R27/C6/R31/C3)을 시도해서 서로 다른 이득(1/4/16/64)으로 최상의 THD와 잡음 성능을 달성하도록 할 수 있다. 최종적인 소자 값은 R22/R27 = 100Ω, C14/C6 = 1nF, R30/R31 = 1.2kΩ, C3/C5 = 0.22µF이다. 아래의 PGIA에서 이득 = 1로 측정된 3dB BW는 약 16kHz이다.

평가 테스트 셋업

잡음, THD, CMRR 성능을 테스트하기 위해 디스크리트 ADA4084-2 PGIA와 AD7768-1 보드를 토털 솔루션으로 제작했다. 이 솔루션은 EVAL-AD7768-1 평가 보드와 호환 가능하며, SDP-H1 제어 보드와 연결할 수 있다. 그러므로 EVAL-AD7768FMCZ 소프트웨어 GUI를 사용해서 데이터를 수집 및 분석할 수 있다.

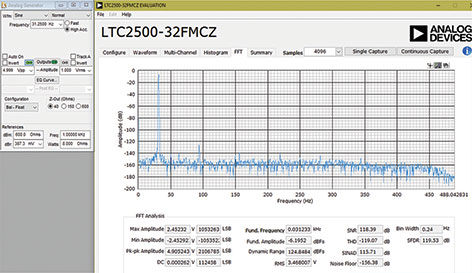

대안적인 토털 솔루션으로, ADA4084-2 PGIA와 LTC2500-32 보드도 제작했다. 이 보드 역시 SDP-H1 제어 보드에 연결할 수 있으며, LTC2500-32FMCZ 소프트웨어 GUI를 사용해서 분석할 수 있다.

[그림 9] ADA4084-2 PGIA와 AD7768-1을 사용한 평가 보드 솔루션

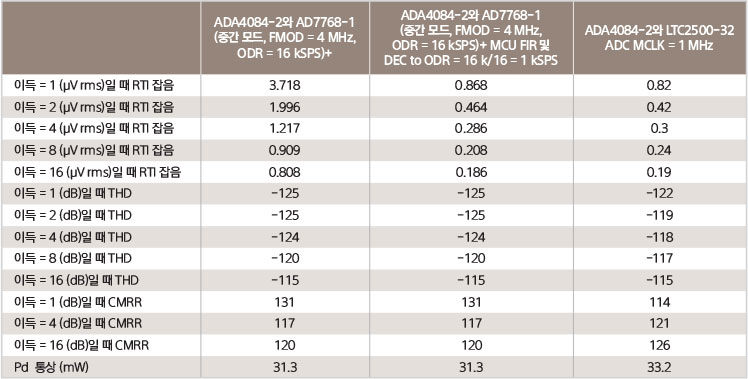

두 보드 모두 PGIA의 이득을 1/2/4/8/16으로 설계했는데, 이는 그림 8에서 보여준 것과는 다르다. 표 5는 이들 두 보드의 테스트 결과를 보여준다.

[표 5] 신호 체인 솔루션 테스트 결과

[그림 10] ADA4084-2 PGIA와 LTC2500-32를 사용한 보드에서 이득= 1일 때 FFT

맺음말

지진 탐사 및 에너지 탐사용으로 잡음이 극히 낮은 저전력 DAQ 솔루션을 설계하기 위해서는, 디스크리트 PGIA를 잡음과 THD가 낮은 정밀 증폭기를 사용해서 고분해능 정밀 ADC를 구동하도록 설계할 수 있다. 이 솔루션은 전력 소모 요건에 맞춰 잡음, THD, ODR을 유연하게 최적화할 수 있다.

• ADA4084-2와 함께 잡음이 낮은 LTC2500-32를 사용하면 MCU의 추가적인 필터링 프로세싱 없이도 우수한 잡음 성능을 달성할 수 있다.

• ADA4522-2와 ADA4084-2 둘 다 PGIA 이득 = 1로 잡음 성능이 약 0.8µV rms로 우수하다.

• 높은 이득의 경우, ADA4084-2가 잡음 성능이 더 우수하다. 이득 = 16일 때 ADA4084-2와 LTC2500-32를 사용하는 솔루션의 잡음은 0.19µV rms이다. 이는 ADA4522-2를 사용하는 솔루션의 0.25µV rms보다 우수하다.

• ADA4084-2와 AD7768-1을 사용하는 솔루션은 MCU 필터링을 사용해서 ADA4084-2와 LTC2500-32를 사용하는 솔루션과 비슷한 잡음 성능을 나타낸다.

이 글에서는 제한적 대역폭으로 낮은 잡음과 저전력 소모를 요구하는 데이터 수집 애플리케이션에 적합한 솔루션들을 살펴봤다. 다른 DAQ 애플리케이션들에서는 성능 요건이 이와 다를 수 있다. 예를 들어서 저전력 소모가 필수 요건이 아닐 수 있다. 이러한 경우에는 다음과 같은 연산 증폭기 제품들을 사용해서 PGIA를 설계할 수 있다:

• 극히 낮은 잡음: 우수한 잡음 성능을 위해서는 LT1124와 LT1128을 사용할 수 있다.

• 극히 낮은 드리프트: 새로운 제로 드리프트 증폭기로서 ADA4523은 ADA4522-2와 LTC2500-32보다 잡음 사양이 우수하다.

• 극히 낮은 바이어스 전류: 센서의 출력 저항이 높을 때는 ADA4625-1이 권장된다.

• 높은 대역폭: 대역폭이 높은 DAQ 애플리케이션에서 높은 대역폭에 잡음이 낮은 PGIA를 설계하고자 할 때는 ADA4807, LTC6226, LTC6228이 좋은 솔루션이 될 수 있다.

잡음과 전력은 그리 중요하지 않지만 작은 PCB 면적과 높은 무결성이 중시되는 DAQ 애플리케이션에는 ADI의 새로운 통합형 PGIA 제품들로서 ADA4254와 LTC6373이 좋은 선택이다. ADA4254는 제로 드리프트, 고전압, 1/16~176 이득을 특징으로 하는 견고한 PGIA 제품이고, LTC6373은 25pA IBIAS, 36V, 0.25~16 이득, 낮은 THD를 특징으로 하는 PGIA 제품이다.

[참고 문헌]

[1] Geophones. ScienceDirect.

[2] Jesse Santos, Angelo Nikko Catapang, and Erbe D. Reyta. “Understanding the Fundamentals of Earthquake Signal Sensing Networks.” Analog Dialogue, Vol. 53, No. 4, December 2019.

[3] Kristina Fortunado. “Programmable Gain Instrumentation Amplifiers: Finding One that Works for You.” Analog Dialogue, Vol. 52, No. 4, December 2018.

레귤레이트 된 48V를 12V로 첫 번째 단의 효율을 대폭 향상시키는 결합 ...

조회수 449회 / Alexandr Ikriannikov 외 1인

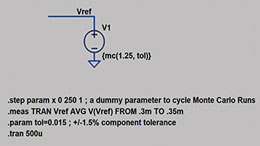

LTspice를 사용하여 복잡한 회로에 대한 통계학적 허용오차 분석 모델링...

조회수 1834회 / Steve Knudtsen

실제 유용한 디지털 전치왜곡 솔루션 설계 방법

조회수 1161회 / Steve Summerfield 외 1인

보다 우수한 성능의 산소포화도 측정기 설계 방법

조회수 8152회 / Robert Finnerty

지진 탐사 및 에너지 탐사 애플리케이션용 저잡음 저전력 DAQ 솔루션

조회수 1213회 / David Guo

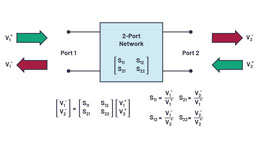

RF 신호 체인의 주요 특성 및 성능 지표

조회수 4680회 / Anton Patyuchenko

PCB 공간 제약 문제 해결하는 모놀리식 벅-부스트 컨버터 및 LED 드라이버

조회수 1663회 / Kyle Lawrence

퍼시비어런스 화성 탐사선과 극한환경을 위한 고신뢰성 기술

조회수 1353회 / Analog Devices

아나로그디바이스(ADI), 반도체 업계 ESG 경영 선도한다

조회수 1255회 / ADI

PDF 다운로드

회원 정보 수정