지터가 고속 링크에 미치는 영향

글/Bill Schweber, 전자엔지니어

클록 발진기는 시스템 부품의 속도를 조정하여 최신 회로의 핵심적 타이밍을 제공한다. 시스템 속도가 수백 메가헤르츠(MHz) 이상으로 증가하면 시스템 성능을 유지하기 위해 이러한 클록이 빨라져야 하고 통상 100fs(펨토초) 이하의 매우 낮은 지터를 제공해야 한다. 또한 온도 및 전압의 변화에도 불구하고 시간의 흐름에 상관없이 낮은 지터 사양을 유지해야 한다.

일부 지터는 신호 경로 잡음 및 왜곡에 의해 유도되며 이는 리클로킹 및 리타이밍 기술을 사용하여 어느 정도 줄일 수 있다. 그러나, 지터는 클록 소스(일반적으로 발진기)에 의해서도 생성된다. 이는 다양한 물리적 현상에 의한 것이며 열 잡음, 프로세스 결함, 전원 공급 장치 잡음, 클록 발진기에 들어가는 기타 외부 잡음, 재료 응력 및 기타 여러 미묘한 요인들이 여기에 포함된다. 그 원인에 상관없이 결함은 되돌릴 수 없기 때문에 설계자는 내재적인 클록 지터를 최소화하기 위해 가능한 모든 작업을 수행해야 한다.

이 글에서는 다양한 관점에서 지터 문제를 논의한다. 그런 다음 Abracon LLC의 다양한 클록 발진기를 소개하고, 클록 발진기 성능을 응용 제품에 일치시켜 지터를 최소화할 수 있는 방법을 보여준다.

지터 기본 사항

클록 지터는 이상적인 시간 위치에서 클록 에지의 편차이다. 이 지터는 클록 신호 속도가 조정되는 데이터 신호 전송의 타이밍 정밀도 및 정확도에 영향을 미쳐 수신기 해독/복조 회로망 또는 다른 시스템 IC에서 신호 대 잡음비(SNR)를 악화시킨다. 이로 인해 비트 오류율(BER)이 높아지고 재전송이 증가되며 효과적인 데이터 처리량이 감소한다.

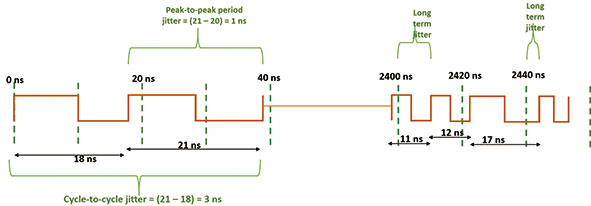

클록 지터의 중요성을 고려할 때 이는 케이블, 커넥터 또는 회로 기판을 통해 송신 소스에서 수신기로 신호를 전달하는 시스템에서 광범위하게 분석된다. 클록 지터는 응용 제품에 따라 사이클 간 지터, 주기 지터, 장기 지터를 비롯한 여러 방법으로 특징지을 수 있다(그림 1).

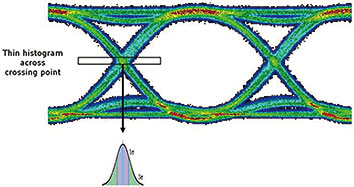

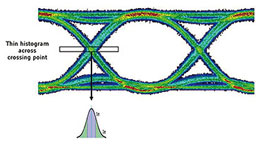

지터는 낮은 BER 데이터 복구를 달성하는 데 사용되는 다른 하위 기능, 부품 또는 시스템에서 사용하는 타이밍을 손상시키거나 동기식 시스템의 메모리 소자 또는 프로세서와 같은 속도 부품을 변질시킬 수 있다. 그림 2의 아이 다이어그램에서는 비트 타이밍의 교차 지점이 넓어지는 것을 볼 수 있다.

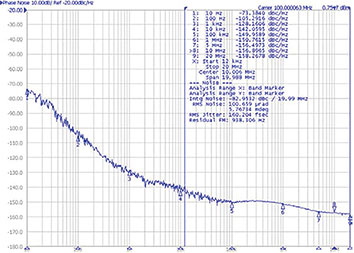

지터는 시간 영역 및 주파수 영역 모두에서 측정할 수 있다. 둘 모두 동일한 현상에 대해 똑같이 유효한 관점이다. 위상 잡음은 발진기 신호 주변의 잡음 스펙트럼에 대한 주파수 영역 표시이고 지터는 발진기 주기의 타이밍 정확도를 시간 영역에서 측정한 값이다.

지터 측정값은 여러 방법으로 표현할 수 있다. 이는 일반적으로 ‘10ps(피코초) 지터’와 같은 시간 단위를 사용하여 인용된다. 제곱 평균(RMS) 위상 지터는 위상 잡음(주파수 영역) 측정값에서 파생된 시간 영역 파라미터이다. 지터는 위상 지터라고도 하여 혼동을 일으킬 수 있지만, 여전히 시간 영역 지터 파라미터이다.

링크 작동 주파수와 해당 클록 속도가 수십 MHz에서 수백 MHz 이상으로 증가함에 따라 클록 소스에서 허용되는 지터는 약 100fs 이하로 감소한다. 이러한 주파수는 광학 모듈, 클라우드 컴퓨팅, 네트워킹 및 고속 이더넷에 적용되며, 이들 모두는 100MHz ~ 212/215MHz의 반송 주파수와 최대 400Gbps(초당 기가비트)의 데이터 전송률을 요구하는 기능 및 응용 제품이다.

수정 관리

안정적이고 지속적이며 정확한 주파수 클록 신호를 생성하는 가장 일반적인 방법은 수정 발진기를 사용하는 것이다. 연결된 발진기 회로는 수정을 지원한다. 여기에는 여러 회로 제품군이 있으며 각각은 다양한 상충 관계를 가집니다. 수정은 1930년대부터 중주파(300kHz(킬로헤르츠) ~ 3MHz) 및 고주파(3MHz ~ 30MHz) RF 대역의 무선 라디오 통신을 위해 이 역할에 사용되었다.

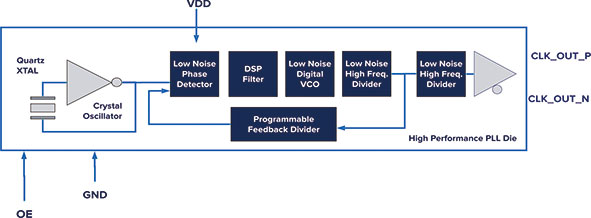

낮은 지터 클록을 생성하는 데 널리 사용되는 접근 방식 중 하나는 PLL 기반 아키텍처의 다양한 변형 중 하나를 사용하는 것이다. 예를 들어 Abracon AX5 및 AX7 ClearClock™ 제품군의 장치는 각각 5mm × 3.2 mm 패키지 및 5mm x 7mm 패키지로 제공되며 뛰어난 저지터 성능을 위해 정교한 PLL 기술을 사용한다(그림 3).

작동 주파수 및 발진기 설계와 함께, 지터 성능은 발진기 코어에 있는 수정의 실제 크기에 의해 영향을 받다. 이 수정의 크기가 줄어들면 우수한 RMS 지터 성능을 제공하기가 더 어려워진다.

100MHz ~ 200MHz 대역의 클로킹 솔루션과 PLL 기반 AX5 및 AX7 장치보다 작은 폼 팩터의 경우 새로운 발진기 아키텍처가 필요하다. 더 작은 크기에 대한 이러한 요구 사항은 일반적으로 최신 광학 트랜시버 및 모듈과 연관이 있다. 100MHz ~ 200MHz 범위의 클록 발진기를 설계하는 방법에는 네 가지가 있다.

① 공진기 소자로 역메사형 석영 블랭크를 갖춘 석영 발진기를 사용한다.

② 공진기 소자로 3차 오버톤 석영 블랭크를 갖춘 석영 발진기를 사용한다.

③ 서브 50MHz, 3차 오버톤/기본 모드 석영 블랭크 또는 정수 또는 분수 모드 PLL IC와 결합된 서브 50MHz, 온도 보상 수정 발진기를 기반으로 하는 발진기 루프를 사용한다.

④ 정수 또는 분수 모드 PLL IC와 결합된 서브 50MHz 마이크로 전자 기계 시스템(MEMS) 공진기 기반 발진기 루프를 사용한다.

옵션 1은 최고의 RMS 지터 성능을 제공하지 않으며, 가장 비용 효과적인 솔루션도 아니다. 옵션 3은 복잡성을 더하고 성능 결함이 있으며, 옵션 4의 MEMS 공진기 접근 방식은 기본 성능 기준인 최대 200fs RMS 지터를 충족하지 않는다. 반면 옵션 2는 전극의 기하학적 구조와 절단 각도의 최적화를 고려하여 최적으로 설계된 3차 오버톤 석영 블랭크를 사용한다. 이러한 조합은 비용, 성능, 크기 측면에서 최적이다.

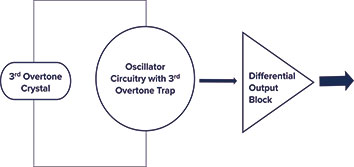

이 접근 방식을 사용하여 Abracon은 ‘3차 오버톤’ ClearClock 솔루션을 개발했다(그림 4). 이 장치는 소음이 더 적은 아키텍처를 사용하여 2.5mm × 2.0mm x 1.0mm의 미니어처 패키지에서 우수한 초저 RMS 지터 성능과 최고의 에너지 효율을 실현한다.

이 아키텍처는 일반적인 PLL 접근 방식을 사용하지 않으므로 상향 변환이 없다. 결과적으로, 표준 PLL 분수 또는 정수 곱셈이 필요하지 않으며 최종 출력 주파수는 3차 오버톤 수정의 공진 주파수와 일대일 상관 관계를 가진다. 분수 또는 정수 곱셈의 부재로 설계가 간소화되고 가능한 가장 작은 크기에서 지터를 최소화할 수 있다.

사양 및 실제 성능

클록 발진기는 수정 및 수정의 아날로그 회로 그 이상이다. 여기에는 발진기 출력 부하와 단기 및 장기 변화가 장치 성능에 영향을 미치지 않도록 하는 버퍼링이 포함된다. 또한 회로 호환성을 위한 다양한 여러 디지털 논리 출력 레벨을 지원한다. 이 호환성 덕분에 외부 논리 레벨 변환 IC가 필요없게 된다. 이러한 IC는 비용, 실장 면적, 지터를 증가시킬 수 있다.

클록 발진기가 서로 다른 레일 전압을 가진 여러 다양한 응용 제품에 사용됨에 따라 이는 일반적으로 2.25V ~ 3.63V에 이르는 맞춤형 값은 물론 +1.8V, +2.5V 또는 +3.3V와 같은 다양한 공급 전압으로 제공되어야 한다. 또한 저전압 포지티브/의사 에미터 결합형 논리(LVPECL) 및 저전압 차동 신호법(LVDS)과 같은 다양한 출력 형식 옵션은 물론 다른 형식에서 사용할 수 있어야 한다.

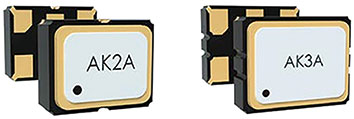

두 가지 수정 클록 발진기 제품군인 AK2A 및 AK3A를 살펴보면 재료, 설계, 아키텍처, 테스트에 대한 정교한 이해와 통합을 통해 무엇을 달성할 수 있는지 확인할 수 있다. 이 두 제품군은 서로 유사하지만 크기 및 최대 주파수에서 두드러진 차이가 있다.

AK2A 제품군: 이 수정 발진기 제품군은 100MHz ~ 200MHz의 공칭 주파수로 제공되며 LVPECL, LVDS 및 HCSL 차동 출력 논리를 갖춘 2.5V, 3.3V, 2.25V ~ 3.63V의 작동 전압에서 사용 가능하다.

이 제품군에 속한 모든 제품은 유사한 성능(예: 저 RMS 지터)을 가집니다. 예를 들어, AK2ADDF1-100.000T는 LVDS 출력과 160.2fs의 RMS 지터를 가진 100.00MHz, 3.3V 장치이다(그림 5). 이 제품의 주파수 안정성은 온도에 걸쳐 ±15ppm(백만분의 1)보다 우수하며 2.5mm x 2.0mm x 1.0mm 크기의 6리드 표면 실장 장치(SMD) 패키지로 제공된다.

AK3A 제품군: AK3A 제품군의 장치는 3.2mm × 2.5mm × 1.0mm 풋프린트를 가진 AK2A 제품군에 비해 약간 크다(그림 6). 이 버전은 AK2A 제품군의 200MHz 제한보다 약간 높은 212.5MHz로 사양이 지정되어 있다.

이 AK3A 장치의 전반적인 사양은 상응하는 AK2A 제품군 장치의 사양과 유사하다. 한 예로 AK3ADDF1-156.2500T3, 156.25MHz LVDS 발진기는 AK2A 제품군의 상응하는 장치보다 약간 뛰어난 통상 81fs의 RMS 지터를 제공한다. 두 제품군의 지터는 작동 주파수, 작동 전압, 패키지 크기, 출력 선택에 따라 달라진다.

실제 상황에서 고려해야 할 사항

공장에서 출고되는 날에만 사양에 맞게 작동하는 클록 발진기를 갖는 것만으로는 충분하지 않다. 모든 부품, 특히 아날로그 및 수동 부품과 마찬가지로 이러한 발진기는 구성 재료의 노후화 및 내부 응력으로 인해 시간이 지남에 따라 드리프트될 수 있다.

이러한 현실은 고성능 클록 발진기의 경우 특히 어렵다. 소프트웨어 또는 고성능 회로를 추가하여 이러한 드리프트를 수정하거나 보상할 수 있는 쉽고 편리한 방법이 없기 때문이다. 그러나, 드리프트의 효과를 완화할 수 있는 몇 가지 방법이 있다. 여기에는 가속화된 발진기 노후화에 대해 최종 사용자가 오랫동안 번인을 수행하거나 오븐 제어 인클로저에서 온도 안정화 발진기를 사용하는 것이 포함된다. 전자의 경우 시간이 많이 소모되고 공급망 문제가 있으며, 후자의 경우 크기가 크며 많은 비용 및 전력이 소모된다.

노후화가 중요한 파라미터임을 인식한 Abracon의 ClearClock 제품군은 10년 ~ 20년의 전체 제품 수명에 걸쳐 엄격하고 포괄적인 주파수 정확도를 제공한다. Abracon은 이 기간 동안 ±50ppm 이상의 주파수 안정도 준수를 보장한다. 이는 3차 오버톤 수정을 신중하게 선택 및 제작하고, -20℃ ~ +70℃에서 ±15ppm 안정성 및 -40℃ ~ +85℃에서 ±25ppm 안정성을 충족하도록 조정함으로써 달성된다.

언제나처럼 엔지니어링은 상호 절충의 과정이다. Abracon AK2A 및 AK3A 계열은 차세대(Gen II) 발진기 ASIC를 사용하여 이전 계열(각각 Gen I AK2 및 AX3)에 비해 향상된 지터-잡음 성능을 제공함으로써 초저 RMS 지터 성능을 보장한다.

이러한 향상은 약간의 전력 소모 증가를 대가로 달성되었다. 최대 전류 소모량은 50mA(Gen I의 경우)에서 60mA(Gen II의 경우)로 증가하지만 저전압 장치는 해당 값의 약 절반을 사용한다. 따라서 2세대 ClearClock 발진기는 초저 RMS 지터를 제공하면서 계속적으로 저전력 소모를 유지한다.

결론

타이밍 발진기는 데이터 링크 또는 클로킹 기능의 핵심이며 정확도, 지터, 안정성은 필요한 시스템 수준 성능(예: 높은 SNR과 낮은 BER)을 달성하는 데 중요한 파라미터이다. 업계에서 요구하는 엄격한 성능 사양과 다양한 표준을 충족하는 혁신적인 재료 선택과 아키텍처를 통해 더 높은 클록 주파수를 달성할 수 있다. Abracon AK2A 및 AK3A 계열은 각 면이 수 밀리미터에 불과한 SMD 패키지로 100MHz ~ 200MHz의 범위에서 100fs 미만의 지터를 제공한다.

재생 가능 에너지를 배터리에 공급하기

조회수 58회 / Bill Schweber

자율 주행 차량의 LiDAR용 GaN FET

조회수 128회 / Kenton Williston

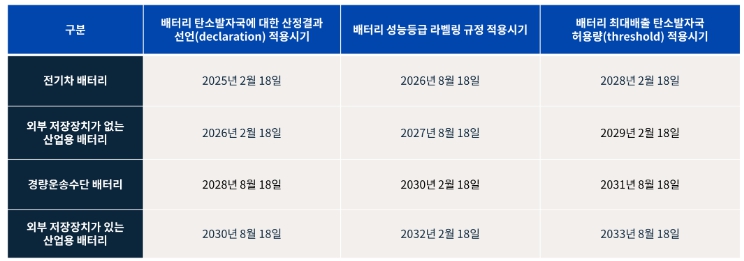

EU 배터리 규정(EU BATTERY REGULATION)이란?

조회수 115회 / TUV

지터가 고속 링크에 미치는 영향

조회수 110회 / Bill Schweber

패널 실장 인코더 - 기본 사항 이해

조회수 346회 / Jeff Smoot

전기 기계 계전기와 무접점 계전기 비교

조회수 300회 / Jeff Smoot

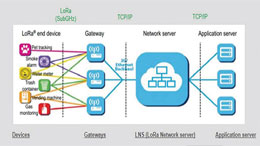

인증된 LoRaWAN 모듈을 사용하여 장거리 연결 개발 가속화

조회수 323회 / Stephen Evanczuk

다양한 응용 제품을 위한 스위치 솔루션

조회수 235회 / Ryan Smoot

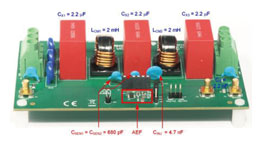

독립형 능동 EMI 필터 IC가 공통 모드 필터 크기를 줄이는 방법

조회수 331회 / 티모시 헤가티

PDF 다운로드

회원 정보 수정